Okika Devices FlexAnalogテクノロジー（旧称 Anadigm Apex 動的プログラマブルアナログ信号プロセッサ（dpASP））は、第3世代の動的プログラマブル・フィールドプログラマブルアナログアレイ（FPAAs）です。FlexAnalogファミリの最初の製品は、7つのアナログ I/O セルと 4 つの構成可能アナログブロック（CAB）を搭載した AN231E04です。

FlexAnalogは、従来の FPAAs 製品と比較して、アナログ性能の向上と価値の向上を実現しています。構成インターフェースは、ダイナミック再構成に対応するように強化されています。これは、アナログ回路の機能をコンパニオンホストプロセッサによって制御できる画期的な機能です。

- ディスクリート部品やASICと比較してソリューションまでの時間を短縮

- システムの劣化や経年変化にもかかわらず高精度な動作を実現

- 複数の製品在庫の調達・維持が不要

- 単一デバイス内で複数のチップ構成を実装可能、かつフィールドでの機能適応を実現

FlexAnalog™ ソリューションにより、OEMは差別化されたソリューションをより迅速に、かつシステム全体のコストを抑えて提供します。

## 法的通知

オキカデバイスは、本資料に記載の製品について、事前の通知なく変更を行う権利を留保します。オキカデバイスは、自社製品の特定の目的に対する適合性について、いかなる保証、表明、または確約も行いません。また、製品または回路の適用または使用に起因する一切の責任を負わず、特に、結果的損害または付隨的損害を含むがこれらに限定されない、あらゆる責任を明示的に否認します。

「標準」パラメータは、異なるアプリケーションにおいて変動する可能性があります。「標準値」を含む全ての動作パラメータは、各顧客アプリケーションにおいて顧客の技術専門家による検証が必要です。

本マニュアルは、当社または第三者の特許権に基づくいかなるライセンスも付与するものではありません。オキカデバイスのソフトウェア及び関連製品は、オキカデバイスのソフトウェアライセンスに厳密に従って使用される場合を除き、使用できません。本規約と矛盾する場合には、該当するオキカデバイスのソフトウェアライセンスの条項が優先されます。

Copyright © 2025 Okika Devices All Rights Reserved

Okika DevicesロゴおよびFlexAnalog<sup>TM</sup>はOkika Devicesの商標です

アナダイムおよびアナダイムデザイナーは、オキカデバイスに買収されたアナダイム社の登録商標です

## 目次

|                              |    |

|------------------------------|----|

| 1. アーキテクチャ概要.....            | 1  |

| 1.1. 動的にプログラム可能なFPAAの使用..... | 2  |

| 1. 標準構成インターフェース接続.....       | 3  |

| 2.1. 動的動作.....               | 3  |

| 2.2. 静的動作.....               | 4  |

| 3. アナログアーキテクチャの詳細.....       | 7  |

| 3.1. タイプ1および1a I/Oセル.....    | 7  |

| 3.2. タイプ2および2a I/Oセル.....    | 8  |

| 3.3. CAB.....                | 9  |

| 4. 構成インターフェースの詳細.....        | 10 |

| 4.1. ピン説明.....               | 10 |

| 4.1.1. セカンダリピン機能.....        | 11 |

| 4.2. 特殊機能 - 設定および制御機能.....   | 12 |

| 4.2.1. リセット.....             | 12 |

| 4.2.2. ERRb.....             | 12 |

| 4.2.3. 監視機関.....             | 12 |

| 4.2.4. アナログおよび構成クロック生成.....  | 13 |

| 4.3. SRAM.....               | 14 |

| 4.3.1. LUT.....              | 14 |

| 4.3.2. 補助セル.....             | 14 |

| 5. 動的操作の詳細.....              | 15 |

| 5.1. 構成データストリームプロトコル.....    | 15 |

| 5.1.1. プライマリ構成フォーマット.....    | 15 |

| 5.1.2. ヘッダーブロック.....         | 17 |

| 5.1.3. データブロック.....          | 18 |

| 5.1.4. 更新フォーマット.....         | 21 |

| 5.2. 設定例.....                | 22 |

| 5.3. 高度な機能 - 論理アドレス指定.....   | 23 |

| 6. パッケージおよびピン情報.....         | 25 |

| 6.1. 推奨されるPCB設計手法.....       | 27 |

## 図表一覧

|                                                            |    |

|------------------------------------------------------------|----|

| 図1 - FlexAnalog <sup>TM</sup> 動的プログラマブルFPAAアーキテクチャの概要..... | 1  |

| 図2 - ホストプロセッサからの単一FPAA構成.....                              | 3  |

| 図3 - ホストプロセッサからの複数FPAAの設定.....                             | 4  |

| 図4 - SPI PROMからの単一FPAAの自己設定.....                           | 4  |

| 図5 - 単一のSPI EEPROMからの複数FPAAの自己設定.....                      | 5  |

| 図6 - タイプ1および1aのI/Oセルオプション.....                             | 7  |

| 図7 - ラウフ入力アンチエイリアシングフィルター.....                             | 8  |

| 図8 - ラウフ出力平滑化フィルタ.....                                     | 8  |

| 図9 - タイプ2および2aの入出力セルオプション.....                             | 9  |

| 図10 - MODEが設定インターフェースの動作を制御する.....                         | 13 |

| 図11 - プライマリ構成データストリーム構造.....                               | 16 |

| 図12 - FlexAnalog <sup>TM</sup> ファミリのデバイス ID .....          | 17 |

| 図13 - AN231メモリ割り当て.....                                    | 19 |

| 図14 - 更新データストリーム構造.....                                    | 21 |

| 図15 - プライマリおよび代替論理アドレス指定.....                              | 24 |

| 図16 - 44ピンQFNパッケージ.....                                    | 25 |

| 図17 - ピン番号と説明.....                                         | 26 |

## 1. アーキテクチャ概要

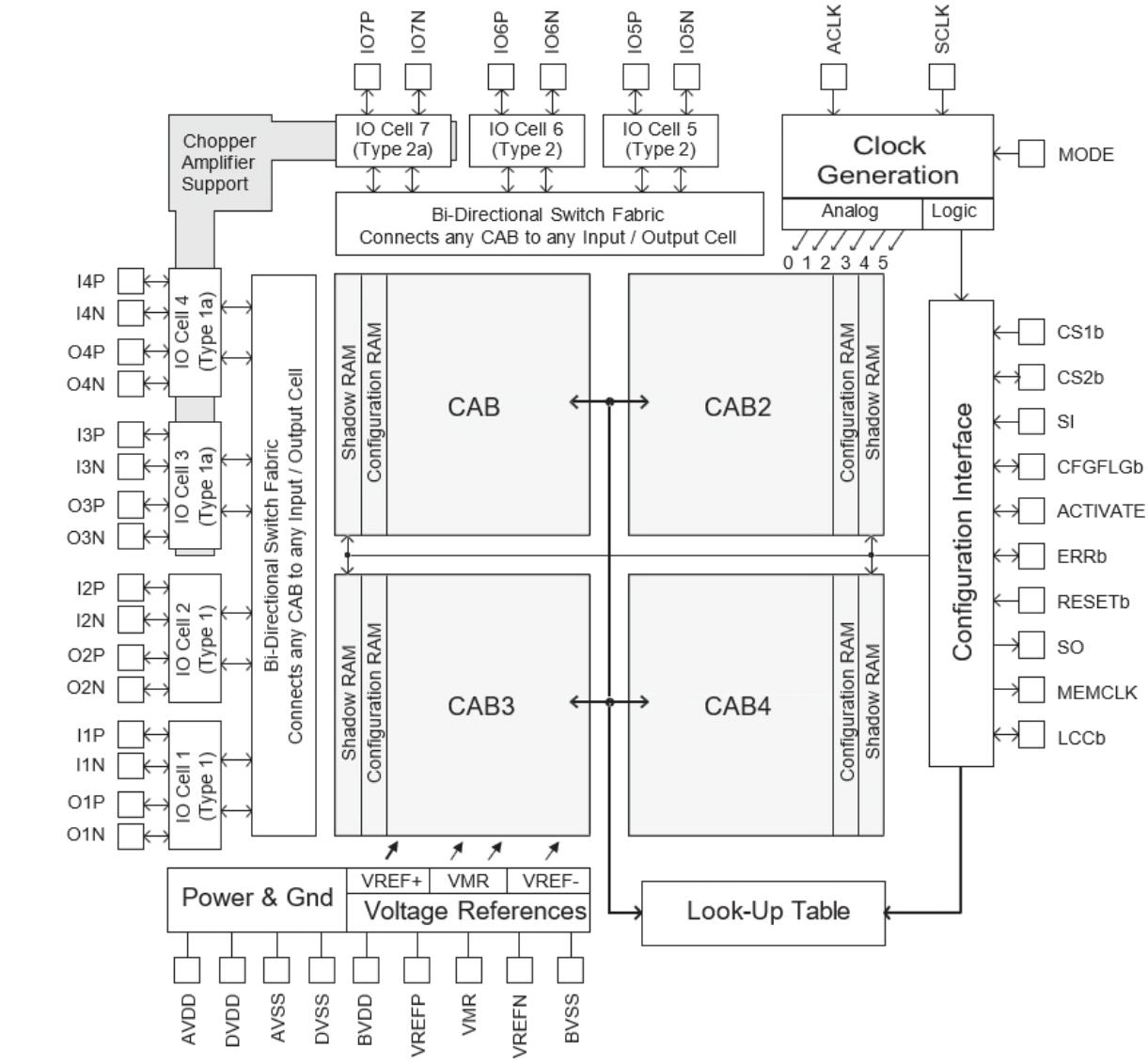

FlexAnalog<sup>TM</sup> ファミリーのFPAAにはAN231デバイスが含まれます。これらのFPAAは、IOセルおよび構成可能アナログブロック(CAB)内でアナログ信号を処理します。これらの構造は、従来型回路要素とスイッチドキャパシタ回路要素の組み合わせで構成され、オフチップの不揮発性メモリまたはホストプロセッサによってプログラムされます。プログラマブルアナログアレイは、従来不可能だったアナログ回路の適応性と柔軟性を実現します。

SRAMベースのAN231は動的に再構成可能である。FPAAの動作は動作中に部分的または完全に変更できる。動的再構成により、コンピニオンホストプロセッサは、旧構成が動作中に新しい構成データをFPAAに送信できます。新しいデータのロードが完了すると、新しいアナログ信号処理構成への移行は1クロックサイクルで実行されます。AN231デバイスにおける動的再構成により、ユーザーは必要に応じて何度もオンラインで更新可能な（完全または部分的な）革新的なアナログシステムを開発できます。

図1 – FlexAnalog<sup>TM</sup> 動的プログラマブルFPAAアーキテクチャの概要

AN231 FPAAはコア内に4つの構成可能アナログブロック（CAB）を備えています。アナログ信号処理の大部分はこれらのCAB内で実行され、完全差動スイッチドキャパシタ回路を用いて行われます。CABは単一のルックアップテーブル（LUT）へのアクセスを共有しており、信号または時間基準に応じてデバイス内の任意のプログラマブルAN231要素を調整する手段を提供します。LUTは任意の入力-出力変換関数（コンパンディング、センサリニアライゼーション）の実装、任意信号の生成、電圧依存フィルタリングの構築にも使用可能です。電圧リファレンスジェネレータはデバイス内の各CABに基準電圧を供給し、フィルタリング用コンデンサ接続用の外部ピンを備えています。

アナログ信号は、利用可能な入出力セルを介してFPAAコアに入り出す：タイプ1が2つ、タイプ1aが2つ、タイプ2が2つ、タイプ2aが1つ。タイプ1およびタイプ1a入出力セルは受動回路と能動回路の両方を備え、直接的な信号入出力、能動フィルタの構築、サンプリング・ホールド回路、デジタル入力、デジタル出力を可能とする。連続時間入力および出力フィルタの応答特性は、内部プログラミングと外部コンポーネントの組み合わせによって決定されます。

タイプ2およびタイプ2aのI/Oセルはより単純で、直接入力および出力、基準電圧出力、デジタル入力、デジタル出力を実装できます。

タイプ1aまたはタイプ2a I/Oセルはいずれも、非常に低エネルギーの入力信号を正確に増幅できる専用のチョッパ増幅器リソースにアクセスできます。

ルックアップテーブル（LUT）機能により、任意波形発生器や非線形伝達関数の構築が可能となります。オンチップ電圧基準生成により、外部基準電圧生成回路が不要となっています。

## 1.1. 動的にプログラム可能なFPAAの使用

FPAA回路の設計はAnadigmDesigner2を用いて行われます。このソフトウェアはグラフィカルな回路設計環境を提供し、基本となるアナログ信号処理のビルディングブロックを配置し配線します。ビルディングブロックには、ゲイン、フィルタ、加算、整流、その他多くの特殊な動作が含まれます。各ブロックの特定パラメータ（利得、コーナー周波数など）はユーザーが設定する。AnadigmDesigner2は構成データファイルを生成する。FPAAの構成データファイルは、スタンドアロン静的動作用のSPI PROMをプログラムするために使用できるほか、ホストされた動的動作用にマイクロコントローラのソースプログラムにコンパイルすることも可能です。

AnadigmDesigner2は、ホストマイクロコントローラ用のCソースコードも生成します。これにより、新しいFPAA構成データのオンザフライ生成と、それに続く動的再構成が可能になります。システムのミッションモードを継続しながら、FPAAの信号処理動作を調整できます。

アナログ回路の動作は、FPAAの設定メモリの内容によって制御されます。このメモリはSRAMベースであり、電源投入後にプログラムする必要があります。FPAAの設定インターフェースは、この目的のためのデータポートを提供します。設定インターフェースは、SPI信号互換のコンパニオンマイクロプロセッサに対してスレーブシリアルデータポートとして動作します。設定インターフェースは、電源投入時またはデバイスリセット後に接続されたSPI PROMから自動的にデータを読み取るよう設定することも可能です。

## 2. 典型的な設定インターフェース接続

AN231デバイス内のアナログ信号処理回路の動作は、その揮発性（SRAMベース）構成メモリの内容によって決定されます。電源投入リセット時、FPAAはメモリをクリアし、デバイスを良性状態に置きます。この電源投入リセットシーケンスが完了すると、デバイスは構成データを受け入れる準備が整います。リセット後にデバイスに最初にロードされる構成データセットは、プライマリ構成と呼ばれます。

AN231デバイスは、後述する更新フォーマットを用いて（リセットを挟まずに）再構成可能です。

設定インターフェースは、シリアルデータマスターまたはシリアルデータスレーブとして動作します。シリアルデータマスターとして、FPAAは接続された業界標準のSPI EEPROMから自動的に設定データセットを取得できます。シリアルデータスレーブとして、FPAAはホストプロセッサからのSPI信号と互換性があり、そのホストから設定データを受け取ることができます。

### 2.1. 動的動作

最も強力なアプリケーション方式は、FPAAをシリアルデータスレーブとして構成した場合である。この動的動作では、コンピニオンホストプロセッサがSPI互換信号を用いてFPAAに構成データを送信する。これにより、動作中に変更可能なアナログ信号処理回路の構築が可能となる。変更内容は、ゲインやコーナー周波数の微調整といった単純なものから、送信機構成から受信機構成への切り替えなど、動作の大幅な変換に至るまで多岐にわたります。

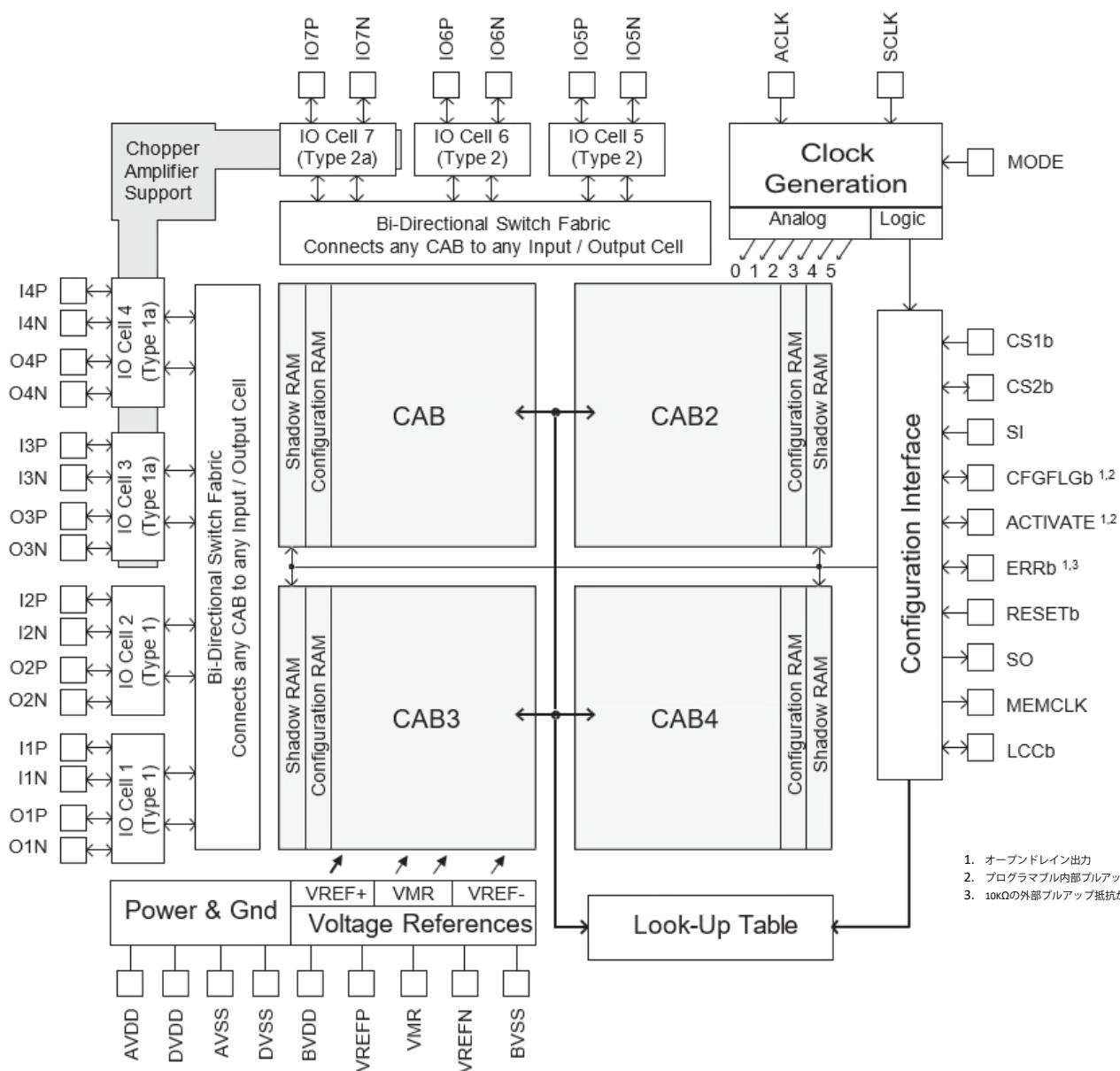

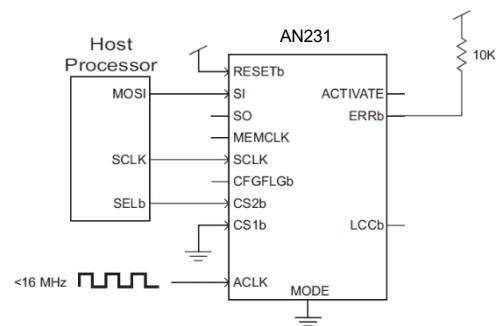

図2：ホストプロセッサからの単一FPAA構成

パワーオンリセット後、FPAAは良性の状態を維持し、構成シーケンスを待機します。FPAAを構成するには、ホストプロセッサがCS2bをローレベルに駆動し、シリアルデータポートから構成データセットをストリーミングします。通常、FPAAは構成終了時に自動的にアナログ信号処理を有効化しますが、他のオプションについては後述します。AN231デバイスは高い柔軟性を備え、リセット後何度でもオンザフライでの再設定が可能です。

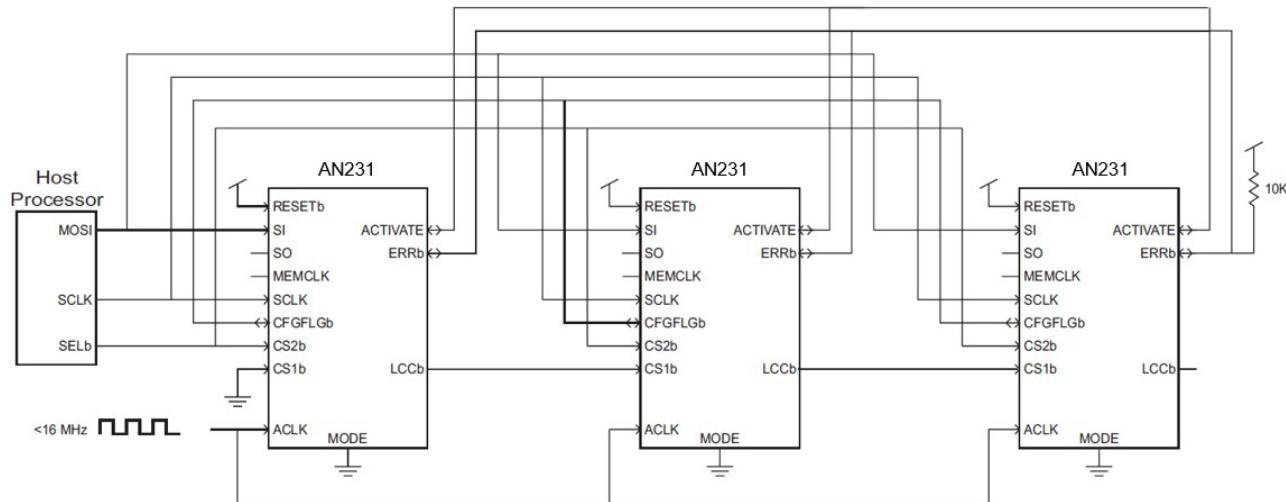

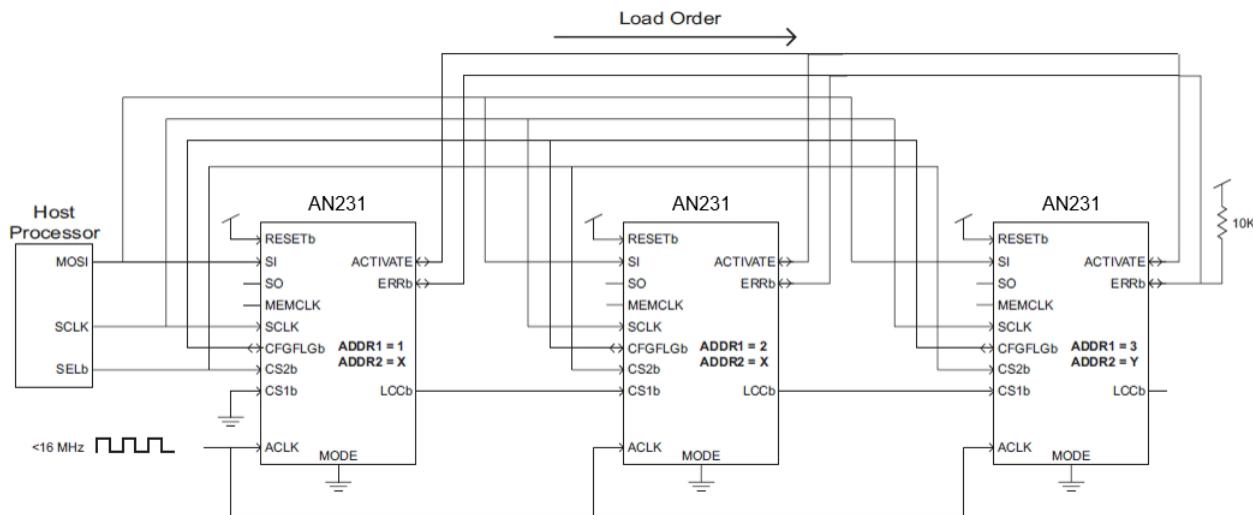

図3：ホストプロセッサからの複数FPAAの構成

ホストプロセッサから複数のFPAAを設定するには、シリアルクロック信号とデータ信号を各FPAAにバス接続するだけで済む。図3は、ホストのMOSI、SCLK、およびセレクト信号を任意の数のFPAAに並列接続した例を示します。

上流デバイスのLCCbピンは下流デバイスのCS1bピンに接続され、上流デバイスが設定を取得するまで下流の設定を保留する。この接続は、後述するCFGFLGbピンの動作と論理アドレス指定と組み合わせて、ホストプロセッサのスレーブデバイス選択出力の節約を可能にする。FPAAの全チェーンでホストからの選択ピンが1本のみで済む点に留意してください。

ACTIVATEノードとERRbノードは、アナログ回路の同時起動を容易にし、設定エラー処理を可能にするため、相互に接続されています。図のように2つ以上のFPAAを接続する場合、CFGFLGbピンをバス接続することが重要です。これらのノードにおけるプルアップ抵抗の使用に関するガイドラインは、後述のセクション2.2に記載されています。

図示はされていませんが、ホストプロセッサがERRbノードを監視するのが一般的な手法です。

## 2.2. 静的動作

静的動作時においては、FPAAは手動リセット後または電源投入時に、SPI PROMから自動的に構成データを読み込みます。

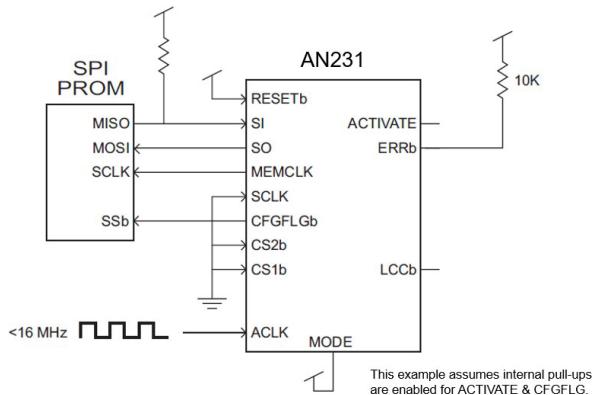

図4：SPI-PROMからの自己自動設定を行なう単一のFPAA

電源入りリセットシーケンスの終了時、CFGFLG<sub>b</sub>はローレベルとなり、接続されたSPI PROMが選択されます。

標準の「読み出し」コマンドがSO (MEMCLKでクロック駆動) から出力されます。MEMCLKが継続する間、SPI PROMはシリアルデータストリームで応答します。このシリアルデータストリームはSIピンで読み取られます。

通常、FPAAは構成完了時に自動的にアナログ信号処理を有効化しますが、その他のオプションについては後述します。

この最も単純な使用モデルでは、FPAAは自動的に：電源投入を検知し、自身をリセットし、標準SPI PROMから設定データを読み込み、アナログ信号処理を開始します。その後のリセットまたは電源サイクルにより、このシーケンスが繰り返されます。

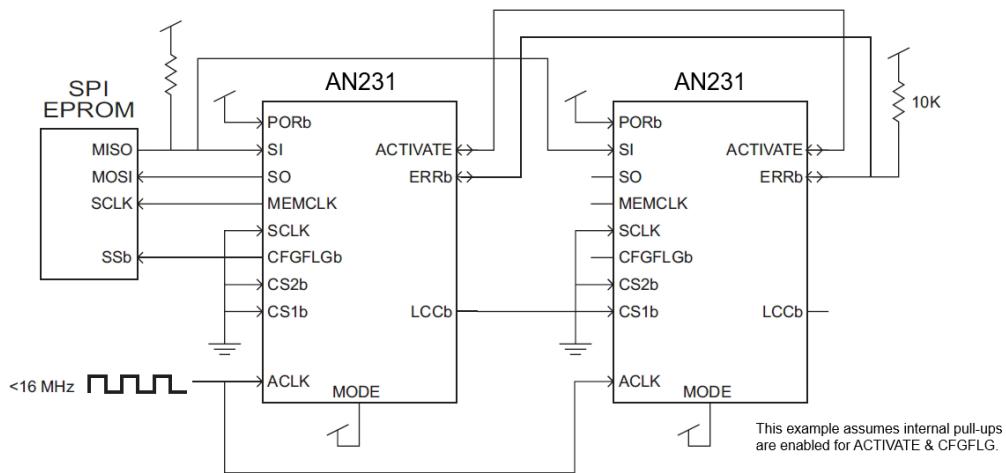

静的構成のやや高度な応用により、複数のFPAAを单一のSPI PROMに接続することが可能となります。この使用シナリオでは、FPAAはデイジーチェーン接続されています。上流側 (PROMに近い) デバイスのローカル構成完了 (LCC<sub>b</sub>) ピンが、下流側デバイスのCS1bイネーブルピンに供給されます。SPI PROMのMISOデータ出力ピンは、全てのFPAAにバス接続され、全てのFPAAはACTIVATEピンとERR<sub>b</sub>ピンを共通化しています。

図5：単一SPI EPROMからの複数FPAAsの自己自動設定

単一のFPAAsの例と同様に、チェーン内の最初のFPAAsは依然としてSPI PROMに対して「read」コマンドを発行しますが、すべてのシリアル設定データに必要なクロック信号を提供します。上流デバイスへの設定が完了すると、そのデバイスのLCCbがローレベルになり、チェーン内の次のデバイス（下流）がデータを受信できるようになります。

ACTIVATEはオープンドレインの双方向ピンです。コンフィギュレーション中はACTIVATEピンがローレベルにアサートされます。アナログ回路はACTIVATEピンがハイレベルに移行するまで有効化（アクティベート）されません。ローカルコンフィギュレーションが完了すると、FPAAsは自身のACTIVATEピンをディアサートし、ACTIVATEノードを監視します。デイジーチェーン接続されたLCCbからCS1bへのシーケンスは、チェーン内の全FPAAsが設定データを受信するまで継続します。この時点で全FPAAsがACTIVATEをディアサートし、共通ラインはプルアップされます。設定チェーン内の全デバイスのACTIVATEピンを接続することで、全FPAAsが設定データを受信するまで、いずれのFPAAsでもアナログ信号処理が開始されないことが保証されます。

ERRbもオープンドレインの双方向ピンです。不正または破損したデータが検出されると、ERRbピンはローレベルをアサートします。構成チェーン内の全デバイスのERRbピンを相互接続することで、いずれかのデバイスがエラーを検出すると、チェーン内の全デバイス（SPI PROMを含む）がリセットされ、構成シーケンスが自動的に再起動するよう保証されます。

#### SIノードのプルアップ

ほとんどのSPI EEPROMは、デバイスが選択されていない場合、MISOピンをトライステート状態に保持します。FPAAsに常に有効な論理信号が供給されるようにするために、SIノードへのプルアップ抵抗の使用が推奨されます。

#### ERRbノードのプルアップ抵抗

ERRbノードには常に $10\text{ k}\Omega$ の抵抗が必要です。

#### ACTIVATE 端子へのプルアップ抵抗

ACTIVATEピンにはプログラマブルな内部プルアップが搭載されています。FPAAsが3つ以下のマスター モードシステムでは、最上流のデバイスでACTIVATEのプルアップを有効にすることを推奨します。4つ以上のFPAAsで構成されるマスター モードシステムでは、ACTIVATEノードに外部プルアップのみを使用してください。

#### CFGFLGb のプルアップ

CFGFLGbピンにはプログラマブルな内部プルアップが搭載されています。CFGFLGbとACTIVATEの内部プルアップは單一の構成ビットで制御され、個別に設定することはできません。したがって、ACTIVATEに適用されるプルアップ規則は、ここでもCFGFLGbに適用されます。

### 3. アナログアーキテクチャの詳細

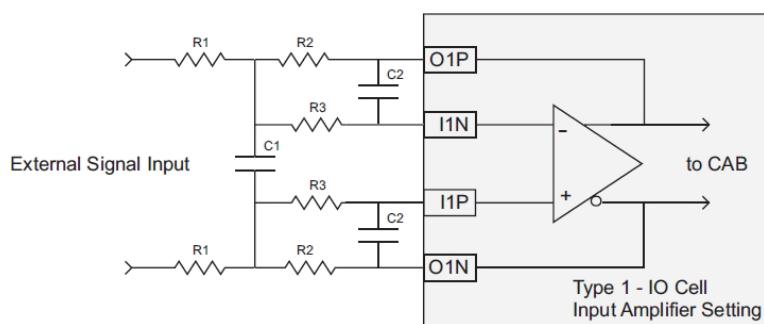

#### 3.1. タイプ1および1a I/Oセル

本デバイスには、タイプ1 I/Oセルが2つ、タイプ1a I/Oセルが2つ搭載されています。これらのI/Oサイトは、CABへの信号入出力において非常に高い柔軟性を提供しています。下図は利用可能なオプションをまとめたものです。

|                                                                       |

|-----------------------------------------------------------------------|

| Bypass I/O                                                            |

| Differential Input                                                    |

| Differential Output                                                   |

| Digital I/O                                                           |

| Differential Input                                                    |

| Differential Output                                                   |

| Analog Input                                                          |

| Amplifier, or                                                         |

| Differential Low Offset Chopper Amplifier (type 1a I/O cell only), or |

| Sample and Hold, with options for input:                              |

| Differential                                                          |

| Inverted Differential                                                 |

| Single Ended Positive                                                 |

| Single Ended Negative                                                 |

| Analog Output                                                         |

| Differential Amplifier                                                |

| Differential Sample and Hold                                          |

| VMR Output                                                            |

| Internal signal reference (1.5 V) presented on both pins.             |

図6：タイプ1 及び 1a I/Oセルのオプション

#### バイパス

I/Oセルのバイパス設定は、CAB入力ポートおよび出力ポートへの直接バッファなしアクセスを提供します。バイパス入力を使用する際は、差動信号と基準電圧がCABと互換性があることを確認する必要があります。差動電圧は0～3Vの範囲で維持し、VMR (1.5V)を中心とする必要があります。

#### デジタル

差動ロジックバッファにより、信号をアレイに入出力できます。この入出力構成は、コンパレータおよびADC-SAR CAMで最も頻繁に使用されます。

#### アナログ入力

アンプの出力は、アンチエイリアシングフィルタの構築および外部ゲイン制御のために外部ピンに提供されます。サンプル・ホールド設定は、I/Oセルのクロックのどちらの位相でも使用できるサンプリング回路を提供します。サンプル・ホールド入力は、差動、反転差動、シングルエンド（正）、シングルエンド（負）として設定できます。

タイプ1a I/Oセルでは、低オフセットチョッパ増幅器設定が利用可能です。チョッパ増幅器は、CAMでの処理前に増幅が必要な微弱な外部信号に対して、非常に低いオフセット電圧を提供するよう特別に設計されています。この設定には、0から40 dBまで10 dBステップでプログラム可能なゲインが含まれます。

構成内の単一のI/Oセルのみが、共有チョッパ増幅器リソースへのアクセスを許可されます。

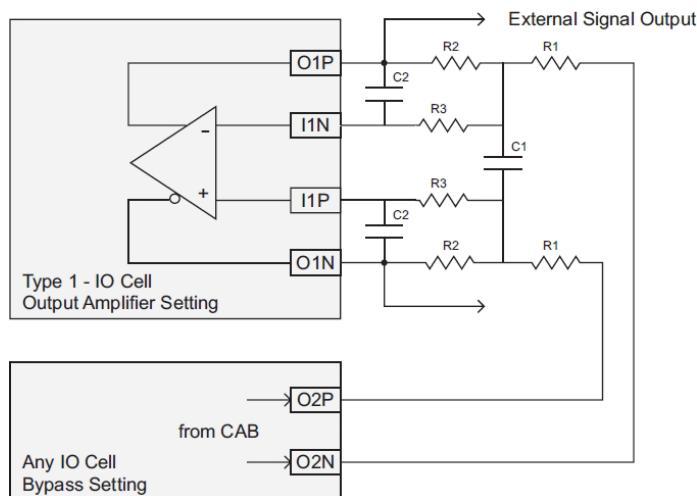

## アナログ出力

アナログ入力と同様に、アナログ出力の設定にはアンプとサンプリング・ホールドが含まれます。アナログ出力からの伝達は常に差動です。アナログ出力のアンプ設定は、I0セルが差動増幅器の入力と出力をデバイスのピンに提示し、外部使用のみに限定するという点で独特です。この設定は、別のI0サイトから供給される差動アナログ信号用の出力平滑化フィルタを作成するために使用されます。

## VMR出力

VMR出力設定は、デバイスの内部信号基準（1.5 V）をI0サイトの2つのピンに接続します。

## アンプ詳細・ラウフ・フィルター設計

タイプ1および1a I0セルのアンプ設定は、連続時間入力アンチエイリアシングおよび出力平滑化フィルタの構築に対応しています。ラウフ（別名：多重フィードバック、MFB）差動フィルタ構成が推奨トポロジです。

図7：ラウフ入力アンチエイリアシングフィルター

同じフィルタ設計手法は、出力平滑化フィルタまたは再構成フィルタの構築にも使用できます。この場合、フィルタ処理されていない出力信号はバイパス出力から供給され、フィルタ構築に使用される増幅器は隣接するI0セルが、その出力増幅器設定を用いて提供します。

図8：ラウフ出力平滑化フィルター

### 3.2. タイプ2および2a I/Oセル

本デバイスには2つのタイプ2および1つのタイプ2a I/Oセルが搭載されています。これらのI/OサイトはCABへの信号入出力において追加の柔軟性を提供します。下図は利用可能なオプションをまとめたものです。

|                                                           |

|-----------------------------------------------------------|

| Bypass I/O                                                |

| Differential Input                                        |

| Differential Output                                       |

| Digital Input                                             |

| Single Ended Input (two per IO Cell)                      |

| Digital Output                                            |

| Single Ended Output (two per IO Cell)                     |

| Chip Clock                                                |

| Comparator                                                |

| RAM Transfer Done                                         |

| Analog Input                                              |

| Low Offset Chopper Amplifier (type 2a IO cell only)       |

| VMR Output                                                |

| Internal signal reference (1.5 V) presented on both pins. |

図9：タイプ2 及び 2aのI/Oセルオプション

#### デジタル入力

2つの独立したシングルエンド論理制御信号をCAMにルーティングできます。

#### デジタル出力

タイプ2 および 2a I/Oセルは、2つのシングルエンド・デジタル出力を提供するように構成できます。出力は、6つの内部クロックのいずれか、コンパレータまたはADC-SAR出力、あるいはシャドウSRAMからコンフィギュレーションSRAMへの転送完了を示す信号を反映することができます。これらの出力信号の極性はプログラム可能です。

#### アナログ入力

タイプ1a I/Oセルと同様に、タイプ2a I/Oセルも低オフセットチョッパー増幅器を備えています。2aチョッパー増幅器は、0~60 dBの範囲で10 dB刻みで設定可能な利得を有します。

### 3.3. CAB (Configurable Analog Block)

アナログ信号処理の大部分は、構成可能アナログブロック（CAB）で行われます。信号処理は、スイッチドキャパシタ回路設計に基づくアーキテクチャを用いて実現されます。各CABには、2つのオペアンプ、コンパレータ、プログラマブルキャパシタのバンク、および構成可能なルーティングとクロックリソースの集合が含まれています。スイッチドキャパシタ信号処理では、チップに集積された部品の絶対値は重要ではなく、採用されたプログラマブルキャパシタとクロック周波数の比率が回路応答を決定します。これら両者は厳密に制御されています。信号忠実度をさらに向上させるため、CAB内の全信号処理は完全差動方式で構成されています。

## 4. 構成インターフェースの詳細

### 4.1. ピン説明

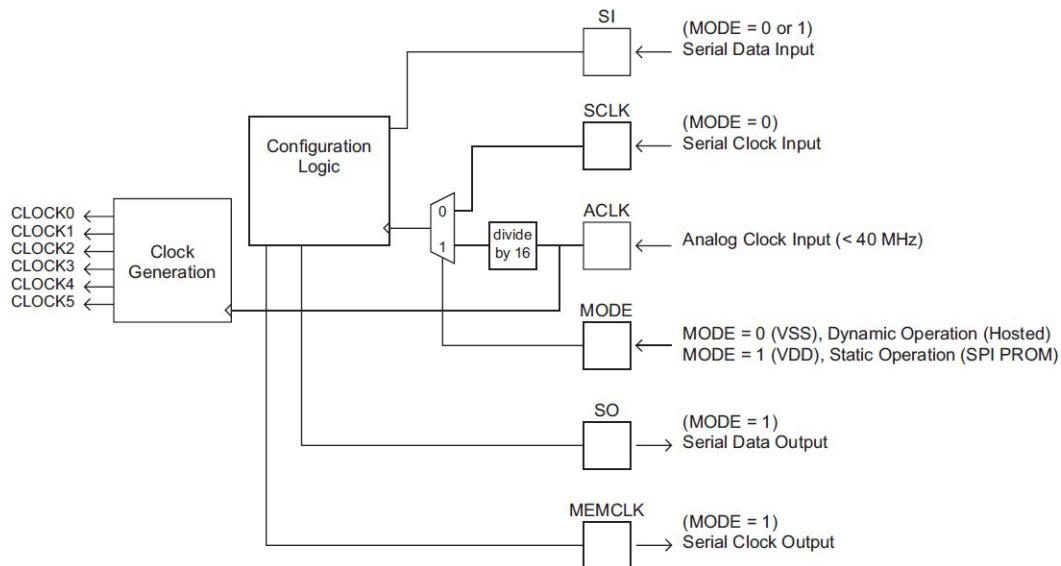

#### MODE

MODEピンの状態は、FPAAの電源投入時リセットシーケンスの一部として読み取られます。リセット解除時にMODEがローの場合、設定インターフェースはシリアルデータスレーブとして動作します。MODEがハイの場合、設定インターフェースはシリアルデータマスターとして動作します。MODEはVDDにハイレベルで接続するか、VSSにローレベルで接続する必要があります。これは静的ピンです。電源投入後の状態変更は許可されていません。

MODEの影響に関する詳細は、セクション4.2.4を参照してください。

#### SCLK (シリアルクロック)

MODEがローの場合、SCLKはシリアルデータクロック入力として機能します。構成ステートマシンはこの入力から駆動されます。SCLKは40MHzを超えてはなりません。SCLKはフリーランニングまたは不連続でも構いません。MODEがハイの場合、SCLKは無視され、コンフィギュレーション状態マシンは内部で分周された ACLK (ACLK/16) によって駆動されます。

#### MEMCLK (メモリクロック)

MODEがハイの場合、FPAAはシリアルデータマスターとして動作します。MEMCLKはシリアルデータクロック出力として機能します。コンフィギュレーション完了後、MEMCLKピンはユーザープログラム可能なデジタル出力として使用可能となります。

#### ACLK (アナログクロック)

ACLKはアナログクロックソースの入力です。すべての内部スイッチドキャッシュタクロックはACLK入力から派生します。ACLKは40MHzを超えてはなりません。MODEがハイの場合、SCLKは無視され、構成状態マシンは内部で分周されたCLK (ACLK/16) によって駆動されます。

#### SI (シリアル入力)

SI ピンは常にコンフィギュレーションデータ入力ピンとして機能します。

#### S0 (シリアル出力)

MODEがハイの場合、S0ピンは接続されたSPI PROMに「読み取り」コマンドを発行します。

#### LCCb (ローカル設定完了)

LCCb (ローカル設定完了) は電源投入リセット中にハイレベルとなり、ローカル設定が完了するまでハイレベルを維持し、その後ローレベルとなります。マルチFPAAシステムでは、LCCb は通常、下流の次のFPAA のCS1b入力に接続されます。コンフィギュレーションが完了すると、LCCb ピンはユーザーがプログラム可能なデジタル出力として使用できます。LCCB はアクティブローです。

次ページへ続く

### CS1b (チップセレクト 1)

CS1bピンもチップセレクト入力として機能しますが、その動作はCS2bよりも複雑です。複数のFPAAシステムでは、CS1b 入力は通常、上流デバイスのLCCbピンによって駆動されます。リセット解除時、上流デバイスのLCCbピンはハイレベルとなり、下流デバイスの設定を一時停止します。上流デバイスがローカル設定を完了しLCCbをローレベルに駆動すると、下流デバイスは設定を開始します。CS1bはアクティブローです。

### CS2b (チップセレクト2)

CS2bピンは通常のチップセレクト入力として機能します。CS2bはアクティブローです。

### CFGFLG<sub>b</sub> (コンフィギュレーションフラグ)

図15に示すように複数のFPAAを接続する場合、各デバイスのCFGFLG<sub>b</sub>ピンを共通ノードに接続する必要があります。CFGFLG<sub>b</sub>ノードは、デバイスが設定または再設定のためにアドレス指定されるたびに（AN23xデバイスのみ）、ローレベルに駆動され、データ転送が完了するとハイレベルにプルアップされます。ローカルデバイスが（他のデバイスによって）CFGFLG<sub>b</sub>がローレベルにプルダウンされていることを検知すると、そのローカルデバイスはSI上のデータを無視します。このCFGFLG<sub>b</sub>信号により、あるデバイス宛ての再構成データが誤って別のデバイスに傍受されることを防止します。

CFGFLG<sub>b</sub>およびACTIVATEの内部プルアップ抵抗を有効にする单一の設定データビットがあります。

### ERR<sub>b</sub> (エラー)

ERR<sub>b</sub>はオープンドレインの双方向ピンです。設定エラーが検出されるたびに、このピンはローレベルをアサートします。マルチFPAAシステムでは、ERR<sub>b</sub>ピンは全て共通接続する必要があります。ローカルデバイスが（他のデバイスによって）ERR<sub>b</sub>がローレベルに引き下げられていることを検知すると、ローカルデバイスはリセットされます。また、ERR<sub>b</sub>信号はパワーオンリセットサイクルにおけるイネーブル信号です。マルチFPAAシステムでERR<sub>b</sub>ピンを共通化することで、全てのデバイスが同時にPORシーケンスを完了できます（ただし、全てのデバイスタイプが同じ時間でパワーオンリセットサイクルを完了するわけではありません）。このピンに関連する動作の詳細については、4.2.2節を参照してください。ERR<sub>b</sub>は外部プルアップ抵抗でハイレベルに保持する必要があります。通常値は10KΩですが、ノード負荷が大きい場合はより低い値でも可。ERR<sub>b</sub>はアクティブローです。

### ACTIVATE

ACTIVATEはオープンドレインの双方向ピンです。単一FPAAシステムでは、ACTIVATEはフローティングのままにできます。プライマリ構成中は、ACTIVATEピンがローレベルにアサートされます。プライマリ構成が完了すると、ACTIVATEは解放され監視されます。ACTIVATEがハイレベルと検知されると、アナログ処理回路がアクティブ化されます。

マルチFPAAシステムでは、ACTIVATEピンは全て共通化されます。ローカルデバイスが自身の設定を完了すると、ACTIVATEをロー駆動するのを停止し、ACTIVATEラインの状態を監視します。全てのデバイスが設定を完了すると、ACTIVATEノードは最終的にハイになり、全てのデバイスがアナログ信号処理を同時に起動できるようになります。ACTIVATE機能に関連する動作の詳細については、セクション4.3.2を参照してください。

CFGFLG<sub>b</sub>およびACTIVATEの内部プルアップ抵抗を有効化する单一の構成データビットが存在します。

### RESET<sub>b</sub>

RESET<sub>b</sub>はアクティブロー入力です。通常、RESET<sub>b</sub>はハイレベルに接続されています。内部のパワーオンリセット回路が電圧低下状態や電源投入状態を検知し、デバイスを自動的にリセットします。アプリケーションで手動リセット機能が必要な場合、このピンをローレベルからハイレベルに駆動することで、完全なパワーオンリセットシーケンスを再起動できます。

#### 4.1.1. 二次ピン機能

LCCbおよびMEMCLK構成ピンは、タイプ2（および2a）I/Oセルで利用可能なプログラマブル極性シングルエンドデジタル出力と同じセットに変換可能です。具体的には：チップロック、コンパレータ、AutoNull/Osc、またはRAM転送完了信号です。

### 4.2. 特殊機能 - コンフィギュレーションおよび制御機能

#### 4.2.1. リセット

デバイスには2種類のリセットがあります。プライマリ・リセットは設定ロジックを安全な起動状態に移行させ、LUTを除くすべてのシャドウSRAMおよび設定SRAMをクリアします。セカンダリ・リセットは設定ロジックのみをリセット状態に移行させ、すべてのSRAM内容は変更されません。

電源投入時、パワーオンリセット回路がプライマリリセットを開始します。この回路は、電圧低下状態が発生した場合や外部RESETbピンがローレベルに駆動された場合にもプライマリリセットを開始します。RESETbピンをローレベルに保持すると、解除されるまでデバイスはリセット状態を維持します。

セカンダリリセットは設定ロジックのみをリセットし、SRAMの内容には影響を与えません。セカンダリリセットの発生源は以下の通りです：ソフトウェアリセット（詳細は5.1.3節参照）および長時間のERRbパルス（詳細は4.2.2節参照）。

#### 4.2.2. ERRb

ERRbピンは複数の異なる機能を果たします。出力として、ERRbがローアサートされると構成エラーを示します。プライマリ構成中に構成データエラーが検出された場合、ERRbは19構成クロックサイクル間ローアサートされます。（スレーブモードでは19 SCLKサイクル、マスターモードでは240 ACLKサイクル。マスターモードではACLK/16が設定ロジックを駆動することを再確認してください。）再設定中の設定データエラーに対するERRb応答（AN23xデバイスのみ）はプログラム可能です。エラー検出時、ERRbのローアサートは5 クロックまたは19クロックのいずれかとなります。「短い」ERRbパルスは、ローカルデバイスがエラーを検出しリセットが発生したことを示します。「長い」ERRbパルスは、共通ERRbノードに接続された全デバイスをリセットさせます。

入力として、ERRbを19サイクル（またはそれ以上）の構成クロックサイクルにわたってローレベルに保持すると、セカンダリリセットが発生します。（手動でリセットをアサートするには、RESETbをパルス状にローレベルにする方法が推奨されます。）

ERRbはまた、電源投入リセットシーケンスの完了を遅延させる制御信号である。電源投入リセットシーケンスの初期段階でERRbはローレベルにアサートされます。シーケンスの終盤でERRbは解放され、監視される。ERRbが有効な論理ハイ状態に達すると、電源投入リセットシーケンスは終了します。すべてのFPAAデバイスタイプが同一長さの電源投入時リセットシーケンスを持つわけではないため、システム内の全FPAAのERRbピンを共通化することで、最遅デバイスが完了するまで全デバイスがリセット状態を維持し、その時点で全デバイスが同時にリセット解除されることが保証される。（詳細は4.2.1節を参照のこと。）

#### 4.2.3. ウオッチドッグ

本デバイスには自動省電力機能が搭載されています。有効化時、このウォッチドッグ回路はプライマリアナログクロック（ACLKピン）の周波数を監視します。ACLKが31.25 kHzを下回ると、デバイスは自動的に電源オフ状態に移行します。ACLKが回復すると、デバイスは直ちに通常の電源状態に戻りますが、通常の信号処理が再開される速度は、現在のCAB設定に依存します。

#### 4.2.4. アナログおよび設定クロック生成

デバイス内の全ての信号処理クロックは、ACLKピンに供給されるアナログマスタークロック信号から派生します。ACLK信号は分割され、2つのシステムベースクロック（SYS1およびSYS2）に分割されます。その除算比は1から510の間です。これら2つのシステムクロックはさらに6つの追加クロックドメイン（クロック0からクロック5）に分割されます。これら6つのアナログ処理クロックはそれぞれ、SYS1またはSYS2をベースクロックとして使用でき、そのベースクロックを1から510までの整数倍でさらに分周します。クロック5とクロック6には、 $0^{\circ}$  から  $360^{\circ}$  の範囲で任意に設定可能な位相遅延機能があります。

2つのベースクロックを持つことで、単一デバイス内に2つの独立したアナログ信号処理回路を構築することが可能となります。

2つの独立したベースクロックの使用は危険を伴う場合もあります。2つのクロックドメインを使用する場合、全てのアナログ信号が完全に自ドメイン内に留まることを確実にしなければなりません。スイッチドキャパシタクロックドメイン間を移動するアナログ信号が、歪みなく伝送される可能性は低いです。

クロック周波数はスイッチドキャパシタ方式アナログ回路の動作における基本パラメータである。設計過程でクロック周波数を変更する場合、設計内に配置された周波数パラメータを持つCAMが依然として意図した動作を維持するよう注意が必要である。例えば、フィルタCAMを駆動するクロックの周波数を変更すると、そのフィルタの周波数応答が変化します。

図10：MODEが設定インターフェースの動作を制御

## 4.3. SRAM

デバイス内には3つの揮発性SRAM領域が存在します。最初の領域であるシャドウSRAMは、コンフィギュレーションまたはリコンフィギュレーション時に書き込みが行われるメモリです。シャドウSRAMは、設定データが設定用SRAMに転送される前の一時的な保持領域として機能します。この2つ目の領域である設定用SRAMは、アナログ信号処理回路の動作を制御します。シャドウSRAMから設定用SRAMへの転送は1クロックサイクルで行われ、アナログ信号経路への干渉を最小限に抑えます。3つ目のメモリ領域はルックアップテーブルです。

### 4.3.1. LUT (Look-Up Table)

本デバイスはルックアップテーブル (LUT) メモリを搭載しています。LUTはコンフィギュレーションSRAMのセル位置に対する置換値を提供します。CABとLUTの組み合わせにより、任意波形合成やテーブルベースのセンサリニアライゼーション機能といった非線形関数の生成が可能です。

### 4.3.2. 補助セル

デバイスにはシャドウSRAMとコンフィギュレーションSRAMの両方が含まれていることを思い出してください。コンフィギュレーションSRAMはアナログ信号処理素子の動作を制御します。デバイスに書き込まれたデータはシャドウSRAMにロードされ、内部信号がコンフィギュレーションSRAMへの転送を有効にするまでそこに保持されます。

プライマリ構成の終了時、アクティベートピンがハイレベルになった場合にのみ転送が行われます。

プライマリ設定が完了すると、AN23xデバイスは後続の再設定データをシャドウSRAMに受け入れることができます（更新プロトコルの詳細は5.1.4節を参照）。シャドウSRAMから設定SRAMへの再設定データ転送のタイミングは、RAM転送セルを介して利用可能な複数の方法のいずれかを使用して厳密に制御できます。

#### 即応 (Immediate)

RAM転送セルの即時設定は、再構成データの外部書き込みが完了するとすぐに、再構成データを構成SRAMに転送することを強制します。

#### イベント駆動 (Event driven)

RAM転送セルのイベント駆動設定では、データ転送を発生させるために内部または外部のデジタル制御信号のいずれかを使用できます。内部イベント信号は通常、コンパレータ出力によって生成されます。

#### イベント駆動およびアーミング (Event driven and armed)

アーミング機能により、データ転送のイベント駆動型トリガーを遅延させることができます。アーミング機能を使用する場合、トリガー端子またはアーミング端子のいずれかを外部から供給できますが、両方を同時に供給することはできません。

#### クロック同期 (Clock synchronization)

クロック同期設定は、すべてのチップクロックが同時立ち上がりエッジとなる時点でのみSRAM転送を強制します。これによりクロック分周器の変更時でもクロック同期が維持されますが、再構成ビットストリーム終了と転送開始の間に遅延が生じます。

ACLKはシステムクロック (SYS1およびSYS2) 用に最大510倍まで分割可能です。これらのCABクロックはさらに最大510倍まで分割できます。極めて稀ではありますが、このようなシナリオでは再構成ビットストリーム終了とSRAM転送の間に非常に長い遅延が生じる可能性があります。

## 5. 動的動作の詳細

アナダイムFPAAの最も強力な使用モデルには、コンパニオンホストプロセッサの使用が含まれます。FPAAはMODEをローに固定して使用されるため、構成インターフェースはSPI互換のスレーブとして動作します。ホストプロセッサは、SPIマスターポートからFPAAへデータをダウンロードする構成タスクの管理に単純に使用できます。AN231デバイスではホスト構成が利用可能です。しかし、プログラマブルアナログの真の可能性は、アナログ信号処理要件の変化に応じてホストプロセッサが動的に新規設定データセットを生成・ダウンロードする場合に最大限発揮されます。この動的再構成機能はAN23xデバイスでのみ利用可能です。「Cコード生成」およびこの強力なアプリケーション手法の詳細については、[AnadigmDesigner2](#)のドキュメントを参照してください。本ユーザーマニュアルでは、ホストプロセッサとFPAA間のインターフェースに関する物理的要件およびプロトコル要件のみに焦点を当てています。

### 5.1. 設定データストリームプロトコル

FPAAがマスター mode またはスレーブ mode のいずれで適用されているかにかかわらず、シリアル構成データストリームは本節で定義されるプロトコルに準拠しなければならない。[AnadigmDesigner2](#)はこのプロトコルに準拠した構成データファイルを生成するため、スレーブ化された SPI PROMからの自己起動という最も単純なケースであっても、デバイスに送信されるデータストリームには必要な情報が全て含まれる。動的アプリケーションでは、ホストプロセッサは適切な設定データを生成し、本仕様で定義されたプロトコルを用いてそのデータをデバイスに転送しなければなりません。構成プロトコルを構成するデータ形式は2つあります：プライマリ構成形式と更新形式です。それぞれについて、以下のセクションで詳細に説明します。

#### 5.1.1. プライマリ構成フォーマット

プライマリ構成は、[AnadigmDesigner2](#)によって生成されるデータのフォーマットであり、電源投入リセット後の初回デバイス設定時に厳密に一度だけ使用しなければならないフォーマットです。リセット解除時、すべてのシャドウ SRAM位置は「ゼロ」にリセットされます。したがってプライマリ構成では、シャドウ SRAMの「1」を必要とする領域にのみデータを送信する必要があります。LUT SRAMは明示的にゼロリセットされません。従って LUT を使用する場合、プライマリ構成は LUT SRAM の初期化にも必要となります。

プライマリ構成データセットは、デバイスがリセット済み（シャドウ SRAM がゼロクリア済み）であることを前提とします。構成を可能な限り効率化するため、プライマリ構成データセットには「1」を書き込む必要があるデータのみが含まれます。

プライマリ構成フォーマットは、ヘッダーブロックに続いて1つ以上のデータブロックで構成されます。ヘッダーブロックには同期バイト、デバイスID、ADDR1、構成制御バイトが含まれます。データブロックにはデータ宛先アドレス情報、構成データバイト数、1~256個の構成データバイトが含まれ、その後単一のデータブロック終端バイトまたは2バイトのCRC16チェックワードが続きます。データはFPAAの最上位ビットからシフトインする必要があります。

|                             | データ                              | バイト名                        | 説明                                                             |

|-----------------------------|----------------------------------|-----------------------------|----------------------------------------------------------------|

| Header Block<br>ヘッダー部       | 11010101 D5                      | SYNC                        | 同期バイト、常にD5                                                     |

|                             | 10110111 B7                      | デバイスID [31:24]              |                                                                |

|                             | 00100000 20                      | デバイス ID [23:16]             | デバイス ID                                                        |

|                             | 00000001 01                      | デバイスID [15:8]               | AN231E04 のデバイス ID は 0xB7200100                                 |

|                             | 00000000 00                      | デバイスID [7:0]                |                                                                |

|                             | XXXXXXXX                         | ADDR1                       | ADDR1バイト、FPAAのプライマリ論理アドレス                                      |

|                             | XXXXXXXX                         | CONTROL                     | 構成制御バイト                                                        |

| Data Block(First)<br>最初、始動部 | 11XXXXXXXX                       | バイトアドレス                     | 開始バイトアドレス (DATA_FOLLOW = 1)                                    |

|                             | XXXXXXXXXX                       | パンクアドレス                     | 開始パンクアドレス                                                      |

|                             | XXXXXXXXXX                       | データカウント                     | データバイト数、00 の値は 256 バイトを指示します                                   |

|                             | XXXXXXXXXX                       | DATA 0                      | 開始アドレス + 0 に書き込むデータバイト                                         |

|                             | XXXXXXXXXX                       | DATA 1                      | 開始アドレス + 1 に書き込むデータバイト                                         |

|                             | 残りのデータバイトはこの領域に入ります...           |                             |                                                                |

|                             | XXXXXXXXXX                       | DATA n                      | 開始アドレス + n に書き込むデータバイト                                         |

|                             | XXXXXXXXXX<br>または 00101010<br>2A | CRC_MSB<br>または<br>データブロック終了 | (バイトアドレスのビット 5 による)CRC16 エラーコードの最上位バイト、または<br>データブロック終了定数 0x2A |

|                             | XXXXXXXXXX                       | CRC LSB                     | CRC16 エラーコードの 10 進数 (使用されている場合)                                |

|                             | 残りのデータブロックはこの領域に入る...            |                             |                                                                |

| Data Block(Last)<br>最後、最終部  | 10XXXXXXXX                       | バイトアドレス                     | 開始バイトアドレス (DATA_FOLLOW = 0)                                    |

|                             | XXXXXXXXXX                       | パンクアドレス                     | 開始パンクアドレス                                                      |

|                             | XXXXXXXXXX                       | データカウント                     | データバイト数、値00は256バイトを指示する                                        |

|                             | XXXXXXXXXX                       | DATA 0                      | 開始アドレス + 0 に書き込むデータバイト                                         |

|                             | XXXXXXXXXX                       | DATA 1                      | 開始アドレス + 1 に書き込むデータバイト                                         |

|                             | 残りのデータバイトはこの領域に入力...             |                             |                                                                |

|                             | XXXXXXXXXX                       | DATA n                      | 開始アドレス + n に書き込むデータバイト                                         |

|                             | XXXXXXXXXX<br>または 00101010<br>2A | CRC_MSB<br>または<br>データブロック終了 | (バイトアドレスのビット 5 による)CRC16 エラーコードの最上位バイト、または<br>データブロック終了定数 0x2A |

|                             | XXXXXXXXXX                       | CRC LSB                     | CRC16 エラーコードの最下位バイト (使用されている場合)                                |

図 1 1 : プライマリー構成データストリーム構造

### 5.1.2. ヘッダーブロック

#### SYNC BYTE

構成ロジックは常に同期ヘッダを期待します。プライマリ構成および更新フォーマットの場合、この同期ヘッダは常に 11010101 (0xD5) です。

#### デバイス ID バイト

すべてのAnadigmデバイスタイプには一意の32ビットデバイスIDが割り当てられています。プライマリ構成時にデバイスIDの一致を要求することは、他のデバイスタイプ向けの構成データが誤ってロードされるのを防ぐ手段です。デバイスIDが期待通りでない状態でプライマリ構成を試行すると、デバイスはERRbをアサートし、データはアレイにロードされません。誤ったデータはデバイス内に高ストレス状態を生じさせ、損傷を引き起こす可能性があります。

|             |   |            |

|-------------|---|------------|

| ファミリーメンバー   | : | AN231E04   |

| 32ビットデバイスID | : | 0xB7200100 |

図 1.2 : FlexAnalog<sup>TM</sup> ファミリーのデバイスID

#### ADDR1 バイト

ADDR1 フィールドは、デバイスの 2 つの論理アドレスのうちの 1 つを設定します。ADDR1 は、デバイスのプライマリ論理アドレスと見なされ、プライマリ構成中にロードされます。代替論理アドレス (ADDR2) はヘッダーブロックの一部ではなく、デバイスの設定データ内で確立されるため、データブロック内で配信されます。システム内のすべての FPAA に論理アドレスを設定することで、多くの FPAA を直列に接続でき（物理的なホスト接続を追加で消費しない）、一度設定すれば、特定のアドレスが割り当てられたデバイスとのみ通信できます。

詳細については、セクション 5.2 を参照してください。

### 5.1.3 データーブロック

制御バイト Control byte

| ビット番号 Bit number              |                                                                                                                     |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 7   6   5   4   3   2   1   0 |                                                                                                                     |

|                               | <b>WRITE</b>                                                                                                        |

|                               | 000:WRITEDATA 100:( 製造時予約済)<br>001:WRITEDATA_CLK 101:( 製造時予約済)<br>010:( 未使用) 110:( 製造時予約済)<br>011:( 未使用) 111:SRESET |

|                               | 定数「0」 必ず「0」に設定すること                                                                                                  |

|                               | 定数「0」 必ず「0」に設定すること                                                                                                  |

|                               | 定数「1」 必ず「1」に設定すること                                                                                                  |

|                               | <b>PULLUPS</b><br>1: 内部プルアップ( 有効)<br>0: 内部プルアップ( 無効)<br>このビットは、CFGFLGb ピンおよび ACTIVATE ピンで内部プルアップを有効にするために使用されます。    |

|                               | <b>ENDEXECUTE</b><br>1: データー転送サイクル終了後、<br>シャドー SRAM の内容が設定用 SRAM に複写されます<br>0:No-Action                             |

#### WRITE (書き込み)

##### WRITEDATA

このコマンドは、構成ロジックに対し、入力データブロックを構成データとして処理するよう指示します。

データストリーム内のクロック分周器設定は無視されます。

##### WRITEDATA\_CLK

このコマンドは、入力データブロック をコンフィギュレーションデータとして扱うようコンフィギュレーションロジックに指示します。データストリーム内のクロック分周設定が適用されます。

##### SRESET

このコマンドはチップリセットを実行します。詳細はセクション4.2.1を参照してください。

#### RESET\_ALL (全リセット)

詳細については、セクション 4.2.1 を参照してください。

#### PULLUPS (プルアップ)

このビットは、CFGFLGb および ACTIVATE 外部ピン上の内部プルアップを選択するために使用されます。PULLUPS はステッキー（一度設定するとリセットされるまで設定状態が維持される）であることに注意してください。これは、マルチFPAAシステムにおいて、どのデバイスに PULLUPS が設定されているかをソフトウェアで追跡する必要を回避するためです。

マルチFPAAシステムでは、PULLUPS を設定するデバイスは1つだけにしてください。多数のFPAAを使用し負荷が問題となる場合、CFGFLGb および ACTIVATE ネットの内部プルアップ抵抗の代わりに、外部プルアップ抵抗を使用することが適切です。

#### ENDEXECUTE (実行終了)

詳細はセクション4.3.2を参照してください。

バイト Byte Address

| ビット番号 Bit number |   |   |   |                                                         |   |   |   |

|------------------|---|---|---|---------------------------------------------------------|---|---|---|

| 7                | 6 | 5 | 4 | 3                                                       | 2 | 1 | 0 |

| BYTEADDRESS      |   |   |   | シャドウ SRAM のバンク内における開始バイトアドレス                            |   |   |   |

| ENABLE CRC CHECK |   |   |   | 1:CCITT-CRC1 エラーチェック（有効）<br>0:DATA BLOCK END チェック（有効）   |   |   |   |

| DATA_FOLLOWS     |   |   |   | 1:構成ロジックにより後続のデータブロックを期待<br>0:このブロックは構成データの最終ブロックであると想定 |   |   |   |

| CONSTANT 1       |   |   |   | 1:必ず定数「1」で設定<br>0:未定義                                   |   |   |   |

バンク Bank Address

| ビット番号 Bit number |   |   |   |                      |   |   |   |

|------------------|---|---|---|----------------------|---|---|---|

| 7                | 6 | 5 | 4 | 3                    | 2 | 1 | 0 |

| BANK ADDRESS     |   |   |   | シャドウ SRAM の開始バイトアドレス |   |   |   |

BYTEアドレスとBANKアドレスのバイトを組み合わせることで、後続の構成データブロックのシャドウSRAM（またはLUT SRAM）ロード開始アドレスが形成される。（これらのバイトは、読み出しコマンドの開始読み出しアドレスを設定するためにも使用される。）デバイス内のメモリは、19行（バンク）×32列（バイト）で構成される。バンク境界やバイト境界を越える際に特別な処理は不要で、自動的に処理されます。デバイスのシャドウSRAMおよびLUT SRAMのアドレス割り当ては下図の通りです。

| バンクアドレス<br>レス | バイトアドレス               |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

|---------------|-----------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | 1<br>F                | 1<br>E | 1<br>D | 1<br>C | 1<br>B | 1<br>A | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 0<br>F | 0<br>E | 0<br>D | 0<br>C | 0<br>B | 0<br>A | 0<br>9 | 0<br>8 | 0<br>7 | 0<br>6 | 0<br>5 | 0<br>4 | 0<br>3 | 0<br>2 | 0<br>1 |

| 00            | 補助RAM 0クロック分周器および電源   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 01            | 補助RAM 1 LUTおよびI/O制御   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 02            | 補助RAM 2 I/Oおよびルーティング  |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 03            | CAB 1 シャドウ SRAM バンク A |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 04            | CAB 1 シャドウ SRAM バンク B |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 05            | CAB 2 シャドウ SRAM バンク A |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 06            | CAB 2 シャドウ SRAM バンク B |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 07            | CAB 3 シャドウ SRAM バンク A |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 08            | CAB 3 シャドウ SRAM バンク B |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 09            | CAB 4 シャドウ SRAM バンク A |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 0A            | CAB 4 シャドウ SRAM バンク B |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 0B-0F         | (工場予約アドレス範囲)          |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 10            | ルックアップテーブル SRAM バンク 0 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 11            | ルックアップテーブル SRAM バンク 1 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 12            | ルックアップテーブル SRAM バンク 2 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 13            | ルックアップテーブル SRAM バンク 3 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 14            | ルックアップテーブル SRAM バンク 4 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 15            | ルックアップテーブル SRAM バンク 5 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 16            | ルックアップテーブル SRAM バンク 6 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 17            | ルックアップテーブル SRAM バンク 7 |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| 18-FF         | (工場予約アドレス範囲)          |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

図13 : AN231メモリ割り当て

## データカウントバイト

このフィールドを0x00に設定すると、このデータブロックに256個のデータバイトが続くことを示します。このフィールドを1から255までの任意の整数値に設定すると、その値に正確に一致する数のデータバイトが続くことを示します。このバイト数は、続く構成データバイト（シャドウSRAMまたはLUT SRAM向けのデータバイト）の数を表すのみで、データブロック終了バイトやCRCバイトは含まれません。

バンク境界を越えるデータ書き込みに特別な要件はありません。バンク境界の越えはデバイス内で自動的に処理されます。

## データバイト

構成データバイト。これは、直前に定義されたBYTEアドレスおよびBANKアドレスバイトで指定されたアドレスから開始し、シャドウSRAMまたはLUTSRAMにロードされるデータです。ブロックあたり最大256個のデータバイトを含みます。

## データブロック終了バイト

バイトアドレスのビット5が0の場合、データバイトの後に期待される唯一のバイトはデータブロック終了数0x2Aである。他の値が読み込まれた場合、ERRbが強制実行され設定プロセスは中止される。

## CRC\_MSB および CRC\_LSB バイト

バイトアドレスのビット5が1の場合、各データブロックの終了時にCRC\_MSBバイトに続いてCRC\_LSBバイトが期待される。16ビットCRCはCCITT標準方程式を用いて以下の式で計算されます。

$$x^{16} + x^{12} + x^5 + 1$$

CRCの計算はホストプロセッサにとって計算負荷の高い作業であり、頻繁には使用されていません。代わりに事前に計算されたルックアップテーブルに基づく計算手法では大幅に高速化できますが、すべての結果を格納するために膨大な記憶領域を必要としますので、採用には入念な注意と検討が必要です。

### 5.1.4. 更新フォーマット

プライマリ構成が完了すると、ホストが通信経路上でデバイスID情報を送信する必要はなくなります（これを送信する構成データストリームはエラーと見なされ、デバイスはERRbを強制実行します）。ホストは、同期ヘッダーと対象デバイス（または対象デバイス群）の有効な論理アドレスのみを送信すれば十分です。残りの情報は、前述のセクション5.1.1で説明した通りです。

プライマリ構成と同様に、更新フォーマットにはデバイス用の完全なデータセットを含める必要はありません。デバイスの部分的な再構成がサポートされています。多くの場合、シャドウSRAMまたはLUT SRAMのアドレスの一部のみに新しいデータが必要です。更新フォーマットは、この新しいデータをデバイスに転送するための効率的な方法を提供します。

|              | データ                                | バイト名                        | 説明                                                                   |

|--------------|------------------------------------|-----------------------------|----------------------------------------------------------------------|

| ヘッダーブロック     | 11010101 D5                        | SYNC                        | 同期バイト、常に D5                                                          |

|              | XXXXXXX                            | 論理アドレス                      | ADDR1、ADDR2、または 0xFF - ターゲットデバイスの論理アドレス。                             |

|              | XXXXXXX                            | CONTROL                     | 構成制御バイト                                                              |

| データブロック (最初) | 11XXXXXX                           | バイトアドレス                     | 開始バイトアドレス (DATA_FOLLOW = 1)                                          |

|              | XXXXXXX                            | バンクアドレス                     | 開始バンクアドレス                                                            |

|              | XXXXXXX                            | データカウント                     | データバイト数、値00は256バイトを指示する                                              |

|              | XXXXXXX                            | DATA 0                      | 開始アドレス + 0 に書き込むデータバイト                                               |

|              | XXXXXXX                            | DATA 1                      | 開始アドレス + 1 に書き込むデータバイト                                               |

|              | 残りのデータバイト (ある場合) はこの領域に入力...       |                             |                                                                      |

|              | XXXXXXX                            | DATA n                      | 開始アドレス + n に書き込むデータバイト                                               |

|              | XXXXXXX<br>または 00101010<br>2A      | CRC_MSB<br>または<br>データブロック終了 | (BYTE ADDRESS のビット 5 による)CRC16 エラーコードの最上位バイト、または<br>データブロック終了定数 0x2A |

|              | XXXXXXX                            | CRC LSB                     | CRC16 エラーコードの最下位バイト (使用されている場合)                                      |

|              | 残りのデータブロック (存在する場合) はこの領域に配置される... |                             |                                                                      |

| データブロック (最終) | 10XXXXXX                           | バイトアドレス                     | 開始バイトアドレス (DATA_FOLLOW = 0)                                          |

|              | XXXXXXX                            | バンクアドレス                     | 開始バンクアドレス                                                            |

|              | XXXXXXX                            | データカウント                     | データバイト数、00 の値は 256 バイトを指示します                                         |

|              | XXXXXXX                            | DATA 0                      | 開始アドレス + 0 に書き込むデータバイト                                               |

|              | XXXXXXX                            | DATA 1                      | 開始アドレス + 1 に書き込むデータバイト                                               |

|              | 残りのデータバイト (ある場合) はこの領域に入ります...     |                             |                                                                      |

|              | XXXXXXX                            | DATA n                      | 開始アドレス + n に書き込むデータバイト                                               |

|              | XXXXXXX<br>または 00101010<br>2A      | CRC_MSB<br>または<br>データブロック終了 | (バイトアドレスのビット 5 による)CRC16 エラーコードの最上位バイト、または<br>データブロック終了定数 0x2A       |

|              | XXXXXXX                            | CRC LSB                     | CRC16 エラーコードの最下位バイト (使用されている場合)                                      |

図 14 : 更新データストリーム構造

## 5.2. 設定例

以下の例はマイクロコントローラホスト型インターフェースを想定しています。データはFPAAの最上位ビットからシフトインする必要があります。空白とコメントはこれらの例における可読性向上のためのみに含められています。

### 主要な設定フォーマット例

```

00000000 //内部パワーアップ完了には40クロックが必要

00000000 //リセットシーケンス

00000000 //NULLプレフィックスデータ。40番目のクロックの後

00000000 //設定ロジックが同期待機状態となる

00000000

11010101 //0xD5が要求される同期ヘッダー

10110111 //0xB7はデバイスIDワードの最上位バイト

00100000 //0x20はデバイスIDワードの3番目のバイト

00000001 //0x01はデバイスIDワードの2番目のバイト

00000000 //0x00はデバイスIDワードの最下位バイト

00000001 //0xFF以外の任意のユーザー割り当てADDR1 (プライマリ論理アドレス)

11000001 //制御バイト

//ENEXECUTEが有効化

//PULLUPSが有効化

//WRITEDATA_CLKがコマンド

11000000 //定数「1」。 DATA_FOLLOW。 開始バイトアドレスは0

00000000 //スタートBANKアドレスは0

00000000 //0x00 バイトカウントフィールドは、256 データバイトが続くことを意味する

data data //最初の設定データバイト

dadada //2番目の設定データバイト

...

data data //256番目の設定データバイト

00101010 //0x2A は期待されるデータブロック終了定数

//これは、シャドウSRAMを完全に埋めるために他のデータブロックが送信される領域

//これらのブロックには追加クロックの前置も、デバイスID、ADDR1または制御バイトも不要

//これらの中間ブロックは全て、下記に示す最終ブロックと同形式

//重要な注意点として、プライマリ構成の最終ブロックのみがBYTE ADDRESSバイト内で

//DATA_FOLLOWビットをクリアしている点

10011110 //DATA_FOLLOWが0にクリアされる。これは、この最終ブロックの転送終了時に、

//シャドウSRAMは構成SRAMにコピーされる。ホスト側で追加の操作は不要

//0x1Eは開始バイトアドレスの例

00010111 //0x17 は開始バンクアドレスの例

00000010 //0x02はこの特定の最終ブロックのバイト数

dadada //最後から2番目の設定データバイト

dadada //最後の設定データバイト

00101010 //0x2A は通常期待されるデータブロック終了定数

00000000 //設定状態の終了には8クロックが必要

//転送を完了させるには通常 NULLデータの1バイト送信によって達成される

```

## 更新フォームの例

```

11010101 //0xD5 は必要な同期ヘッダー

00000001 //論理アドレス - ターゲットデバイスの ADDR1 または ADDR2 の値

//またはユニバーサル論理アドレス 0xFF

11000000 //制御バイト

//ENEXECUTEが有効化

//PULLUPSが有効化

//WRITEDATAがコマンド

10011110 //DATA_FOLLOWが0にクリアされているため、設定ロジックはこの最終ブロックの後に

//データが来ないと予想される。また、制御バイトでENEXECUTEが「1」に設定されているため

//シャドウSRAMは設定SRAMにコピーされる。データブロックがダウンロードされるとすぐに

//ホスト側で追加の処理を必要とせずにダウンロード

//0x1E (10進数で30) は開始バイトアドレス

00000011 //0x03 はバンクアドレス開始

00000011 //0x03 バイトカウントフィールドは、3データバイトが続くことを意味する

dadadada //最初の更新データバイトはバンク3のバイト300に格納

datadata //2番目の更新データバイトはバンク3のバイト31に格納

datadata //3番目の更新データバイトはバンク4のバイト0に格納

00101010 //データブロック終了定数 0x2A が期待される

00000000 //必要なクロックを供給するための8ビットの「無関係」NULLビットロードを完了させるために

//必要なクロックを供給するため。EXECUTEビットがこのブロックの制御バイトに設定される。

//直近のシャドウSRAMから設定SRAMへの転送がここで発生する

```

これらの設定例末尾にある8クロックは、その時点での転送完了にのみ必要です。特定の瞬間に転送を完了させる必要性がなければ、後続ブロックに関連するクロックのみで転送は完了します。クロックがなければ、設定ステートマシンはその場で凍結します。「危険な状態・unsafe」は存在しません。

### 5.3. 高度な機能 - 論理アドレス指定

ホストされたマルチFPAAシステムでは、物理的に各デバイスを一意にアドレス指定することが可能です。具体的には、各デバイスのCS2b入力に固有の接続を割り当てることで実現します。ただしこの方法では、ホストプロセッサのチップセレクト出力ピンを消費し、ホストソフトウェア設計が複雑化します。これに対し、Anadigm FPAAは全FPAAを単一のSPIバス上に配置し、共通のチップセレクトを共有しながらデータストリーム内の論理アドレスに応答する機能を備えています。AnadigmDesignerでの設計時には、各チップインスタンスに関連付けられたデータ入力フィールドを用いて、ADDR1（プライマリ論理アドレス）とADDR2（代替論理アドレス）を設定します。

デバイスのプライマリ論理アドレスは、プライマリ構成データストリームのADDR1フィールドで設定されます。デバイスの代替論理アドレス（ADDR2）は、同じデータストリーム内の後続の構成データブロック内で設定されます。プライマリ構成が完了すると、デバイスは次のいずれかを包含する更新再構成データストリームに応答します：一致する ADDR1値、一致するADDR2値、またはLOGICAL ADDRESSバイトフィールド内の0xFF。16進アドレス0xFFはグローバル論理アドレスとして機能し、すべてのデバイスがこのIDに応答します。これはADDR1やADDR2の値に関係なく適用されます。

図15：プライマリ及び代替論理アドレス指定

図15は、単一のSPIポートからホストされる複数のFPAAに対する有効な接続および構成例を示しています。この例では、プライマリ構成中に、チェーン内の各デバイスは一意のADDR1と非一意のADDR2を受け取りました。ADDR1は、プライマリ構成データストリームのADDR1フィールドを介して割り当てられました。ADDR2は、各デバイスにダウンロードされた構成データセット内で確立されました。これら全てのデバイスに対するプライマリ構成が完了すると、各デバイスは、更新構成データストリームのLOGICAL ADDRESSフィールドに自身のADDR1またはADDR2識別子（または0xFF）が含まれている場合にのみ、ホストSPIポートに応答します。

2つのデバイスが同一のアナログ機能「X」を実行し、3つ目のデバイスが固有の機能「Y」を実行すると仮定する。また、XとYの構成データセットにはそれぞれXとYのADDR2値が含まれていると仮定する。プライマリ構成中、ホストプロセッサは最初のデバイスにADDR1=1を割り当て、そのデバイスにX構成を書き込んだ。同様に、ADDR1=2のデバイスにもX構成が割り当てられた。ADDR1=3のデバイスにはY構成が割り当てられた。これらのプライマリ設定が完了しアナログ動作が開始されると、ホストプロセッサは更新処理において、論理アドレス=1→論理アドレス=2と順次アドレス指定する代わりに、論理アドレス= Xを使用することで両Xデバイスを同時に変更できる。ホストが論理アドレスフィールドに0xFFを使用した場合、3つのデバイス全てが後続の再設定データを同時に受け入れる。

#### マルチFPAAシステムにおけるCFGFLGbピンの接続

図15に示すように複数のFPAAを接続する場合、各デバイスのCFGFLGbピンを共通ノードに接続する必要があります。CFGFLGbノードは、デバイスが設定または再設定のためにアドレス指定されるたびに（AN23xデバイスのみ）、ローレベルに駆動され、データ転送が完了するとハイレベルにプルアップされます。ローカルデバイスがCFGFLGbが（他のデバイスによって）ローレベルにプルダウンされていることを検知すると、SI上のデータを無視します。このCFGFLGb信号により、あるデバイス向けの再構成データが別のデバイスに誤って傍受されるのを防ぎます。

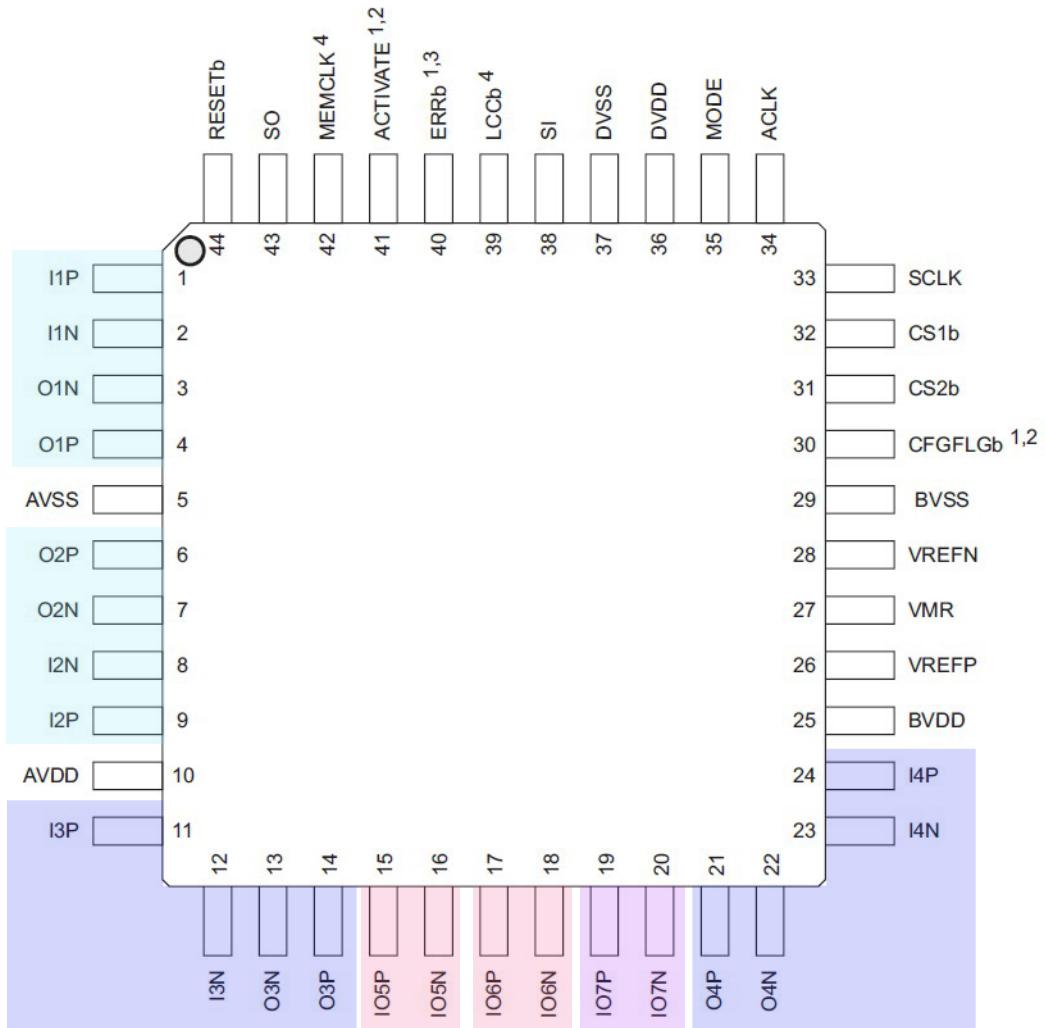

## 6. パッケージおよびピン情報

図 1 6 : 44QFNパッケージ

### I/Oの属性

Type 1

Type 1a

Type 2

Type 2a

1:Open Drain Output

2:Programable Internal Pull-up

3:10kΩ External Pull-up Required

4:Optional Digital Output After Configuration

| ピン | 名称                  | 説明                                                              |                      |

|----|---------------------|-----------------------------------------------------------------|----------------------|

| 1  | I1P                 | 正入力                                                             | I/Oセル 1<br>(Type 1)  |

| 2  | I1N                 | 負入力                                                             |                      |

| 3  | O1N                 | 負出力                                                             |                      |

| 4  | O1P                 | 正出力                                                             |                      |

| 5  | AVSS                | アナロググランド (0 V)                                                  |                      |

| 6  | O2P                 | 正出力                                                             | I/Oセル 2<br>(Type 1)  |

| 7  | O2N                 | 負極出力                                                            |                      |

| 8  | I2N                 | 負入力                                                             |                      |

| 9  | I2P                 | 正入力                                                             |                      |

| 10 | AVD                 | D アナログ電源 (3.3 V)                                                |                      |

| 11 | I3P                 | 正入力                                                             | I/Oセル 3<br>(Type 1a) |

| 12 | I3N                 | 負入力                                                             |                      |

| 13 | O3N                 | 負出力                                                             |                      |

| 14 | O3P                 | 正の出力                                                            |                      |

| 15 | I05                 | P 入力／出力                                                         | I/Oセル 5<br>(Type 2)  |

| 16 | I05                 | N 負入力/出力                                                        |                      |

| 17 | I06                 | P ポジティブ入力/出力                                                    | I/Oセル 6<br>(Type 2)  |

| 18 | I06                 | N 負入力/出力                                                        |                      |

| 19 | I07                 | P ポジティブ入力/出力                                                    | I/Oセル 7<br>(Type 2a) |

| 20 | I07                 | N 負入力/出力                                                        |                      |

| 21 | O4P                 | 正出力                                                             | I/Oセル 4<br>(Type 1a) |

| 22 | O4N                 | 負出力                                                             |                      |

| 23 | I4N                 | 負入力                                                             |                      |

| 24 | I4P                 | 正入力                                                             |                      |

| 25 | BVDD<br>VREFP       | バンドギャップ電源 (3.3 V)<br>ノイズダンプ - VREFP と                           |                      |

| 26 |                     | BVSS                                                            |                      |

| 27 | VMR<br>VREFN        | ノイズダンプ - VMR と BVSS の間に 100 nF のコンデンサを取り付ける<br>ノイズダンプ - VREFN と |                      |

| 28 |                     | BVSS                                                            |                      |

| 29 | BVSS                | バンドギャップ接地 (0 V)                                                 |                      |

| 30 | CFGFLG <sub>b</sub> | 1, 2 設定フラグ                                                      |                      |

| 31 | CS2b                | チップセレクト 2 アクティブロー                                               |                      |

| 32 | CS1b                | チップセレクト 1 アクティブロー                                               |                      |

| 33 | SCLK                | デジタルクロック入力                                                      |                      |

| 34 | ACLK                | アナログクロック入力                                                      |                      |

| 35 | MODE                | 4 1 = 静的動作、0 = 動的動作                                             |                      |

| 36 | DVDD                | デジタル電源 (3.3V)                                                   |                      |

| 37 | DVSS                | デジタルグランド (0V)                                                   |                      |

| 38 | SI                  | シリアル入力                                                          |                      |

| 39 | LCC <sub>b</sub>    | 5 ローカル設定完了 アクティブ・ロー                                             |                      |

| 40 | ERR <sub>b</sub>    | エラーフラグ (アクティブロー)                                                |                      |

| 41 | ACTIVATE            | 1, 2 デバイスをアクティブ化                                                |                      |

| 42 | MEMCLK              | SPI マスター mode EEPROM データクロック出力                                  |                      |

| 43 | SO                  | 5 シリアル出力<br>電源投入時リセット入力 (アクティブ・ロー)                              |                      |

| 44 | RESET <sub>b</sub>  |                                                                 |                      |

図 17 ピン番号と説明

注記:

1. オープンドレイン出力

2. プログラマブル内部プルアップ

3. 10KΩの外部プルアップ抵抗が必要

4. 設定後のオプションデジタル入力

5. 設定後のオプションデジタル出力

## 6.1. 推奨PCB設計手法

PCB設計では、対象システムにおけるデジタル信号環境とアナログ信号環境の良好な分離を確保するため、以下の特徴を含める必要があります。優れたPCB設計手法では、デジタル電源プレーンとアナログ電源プレーン、およびグランドプレーンを分離することが求められます。これらのプレーンを基本的に同じ電位で維持することが重要ですが、デジタルプレーンに通常伴うノイズがアナログプレーンにカップリングされるのを防ぐよう注意を払う必要があります。2つのプレーン間の電気的接続は、通常、フェライトビーズでチョーク処理されたワイヤを介して1点のみで実施されます。フェライトビーズはローパスフィルタとして機能します。

混合信号基板設計では、デジタル信号（特にエッジレートが高いデジタル信号）をデジタル電源プレーンとグランドプレーン上のみに配線することが望ましい。エッジレートが高いデジタル信号をプレーン境界に対して垂直に配線しないよう注意が必要である。そうすると境界に沿って両プレーンにノイズ波面が（左右に）発生します。

デジタル電源DVDDはセラミックコンデンサを用いてDVSSへバイパスすることを推奨します。通常、 $0.1\ \mu F$ コンデンサと $0.01\ \mu F$ コンデンサの並列接続で十分です。バイパスコンデンサ接続はインダクタンス低減のため、可能な限りパッケージ近傍で行うこと。このバイパス方式はBVDD-BVSS、AVDD-AVSSペアに対しても同様に有効です。

複数のFPAAシステムでは、全デバイスのVMRノードを共通ノードに接続する必要があります。VMRを有効にするのは1台のデバイスだけで、他の全デバイスではVMRを無効にし、この1台を基準発生器として使用します。これによりシステム内の全デバイスが共通の基準電圧を使用し、デバイス間で発生する可能性のあるオフセット誤差を排除できます。

詳細は [www.okikadevices.com](http://www.okikadevices.com) をご覧いただきか、Okika Devices テクニカルサポートまでメールでお問い合わせください。 [contact@okikadevices.com](mailto:contact@okikadevices.com)