## FPAA で構成するオーディオ用フィルタ設計例

オーディオ帯域（約 20 Hz～20 kHz）向けのアクティブ・フィルタを、FPAA の構成要素（可変ゲインアンプ、スイッチドキャパシタ、オペアンプセル）で組むと、特性の再構成が容易で評価が速く済みます。以下に、用途別の代表例と具体的な値決め、安定動作の要点をまとめ、自動設計ツール AnadigmDesigner2 の画面を元に説明します。アクティブ・フィルタは受動 1 次より高次で急峻な減衰が得られるため、オーディオラインや DAC 後段での帯域外ノイズ抑制に有効です。

### 設計ターゲットと選択指針

ターゲット帯域：オーディオ用途は可聴帯域の端に近い急峻な減衰が重要

(例：DAC の  $fs/2$  近傍のイメージやクラス D の高調波を可聴帯域外に追いやる)。

フィルタ種別の選び方：

ローパス (LPF) :

高域ノイズ・量子化イメージ対策、サブウーファ用ライン。

ハイパス (HPF) :

DC オフセット除去、低域ハム対策。

バンドパス (BPF) / ノッチ：

特定帯域の成形またはハウリング対策。オーディオでよく使うのは LPF/HPF を 2～4 次で組む構成です

### 実装・評価の実用ポイント (FPAA+オーディオ)

帯域外ノイズへの目配り：DAC のノイズシェーピングで帯域外へ追い出された成分やクラス D の高調波は、後段のアクティブ・フィルタで可聴帯域に回り込まないよう減衰を確保する設計が重要です。

次数と GBW/スルーレート：オーディオ帯域で 2～4 次を採用する場合、フィルタ段の合成ゲインと位相余裕を見て、十分な GBW のアンプセルを選定します。FPAA の内部アンプ仕様に依存しますが、設計ノートでは 1 MHz 以下の領域でのアクティブ・フィルタ利用が一般的と解説されています。

部品一致・誤差管理：Q のばらつきを抑えるには R/C の一致が重要。FPAA の可変素子 / デジタル制御でパラメータを微調整できると試作段階の歩留まりが向上します

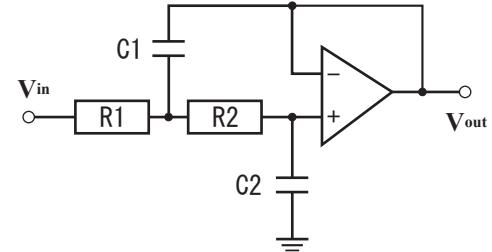

## 設計例 1：DAC 後段の 2 次アクティブ・ローパス（サレン・キー型）

目的：可聴帯域内で平坦、 $f_c$  直上から急峻に減衰（バターワース特性）

設計式（同一値条件）：

$$f_o = \frac{1}{2\pi RC} \quad \text{ユニティゲインで } Q = \frac{1}{\sqrt{2}}$$

設計例 ( $f_c \approx 23$  kHz 近傍、オーディオ DAC 後段)：

- 目標：可聴帯域 20 Hz~20 kHz でフラット、23 kHz で-3 dB 程度。

- 例値： $R1=R2=3.3k\Omega$ ,  $C1=C2=2.2nF \rightarrow f \approx 22$  kHz

- 推奨：GBW が十分なアンプセルを選ぶ (FPAA のオペアンプセルまたは外付けオペアンプで  $GBW > 1$  MHz 程度)。

実装ポイント：

- スイッチドキャパシタ型を使う場合はクロック依存ノイズの帯域外化が可能だが、オーディオ帯域での位相遅れ・残留ノイズを要評価。

- $R/C$  は同一系列で選び、 $\pm 1\sim 5\%$  の誤差で  $Q$  ずれを許容設計。

- クラス D アンプの高調波干渉を想定するラインでは、LPF を後段に追加して帯域外ノイズを抑える

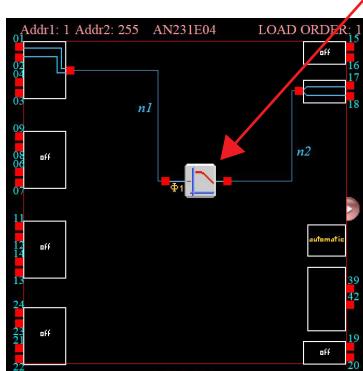

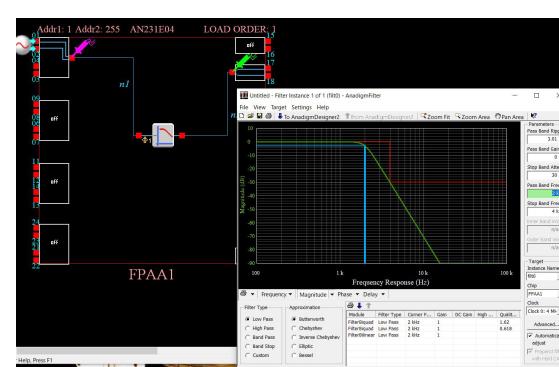

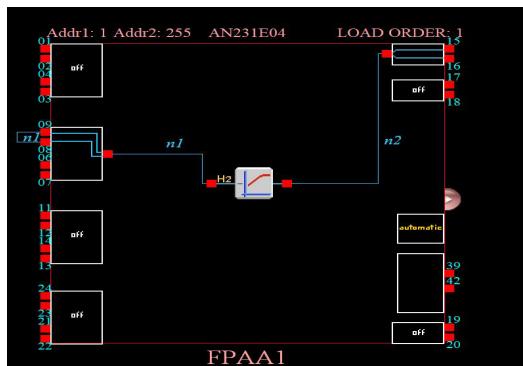

図：LPF 例

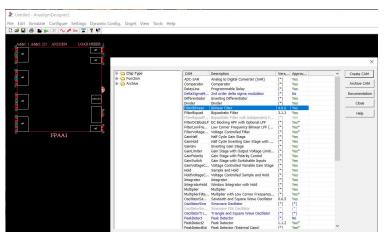

Step1: フィルター種類を選ぶ

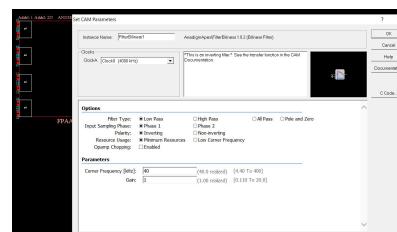

Step2: フィルター諸元設定

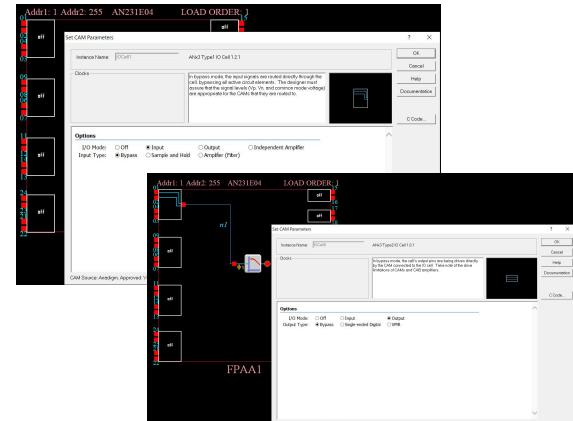

Step3: 使用する I/O の定義

Step4: 結線 (Manual)

Step5: AnadigmFilter で特性確認、及び調整

※：ページは機能を示したものであり、回路図、文章部、下部の図に相互互換性はありません。

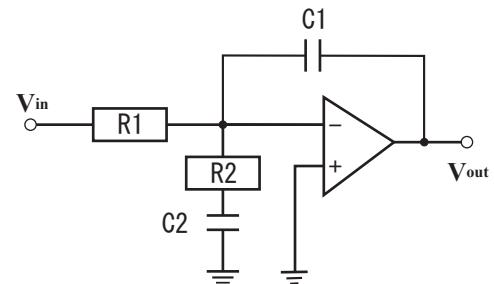

## 設計例2：ライン用ハイパス (DC ブロック、2次)

目的：DCオフセットとサブソニックの抑制、可聴帯域の低域は自然に通す。

### 設計式（目安）：

$$f_c \doteq \frac{1}{2 \pi R_2 C_2}$$

### 設計例 (fc ≈ 20Hz バターワース) :

- $R_2 = 160\text{k}\Omega$   $C_2=50\text{nF}$   $\rightarrow F_c \doteq 20\text{Hz}$

- 比に合わせて、 $R_1$ 、 $C_1$  を設定（標準比で  $Q=0.707$  に調整）

### 実装ポイント：

- ・低域の位相遅れを最小化するため、必要最小限の字数に留める。

- ・電解コンデンサを避け、フィルム / セラミックを優先。

大容量が必要なら誤差と温度特性に注意。

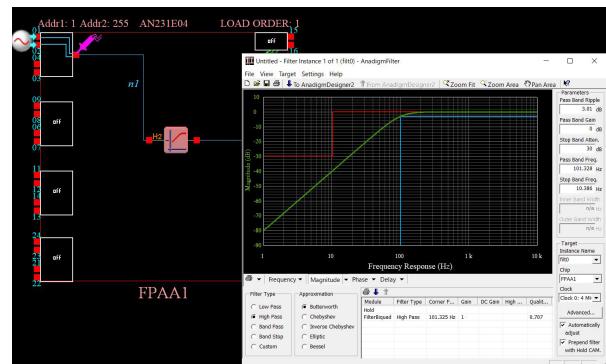

### 図：HPF 例

※: ここまで操作は Page-2 と同じ

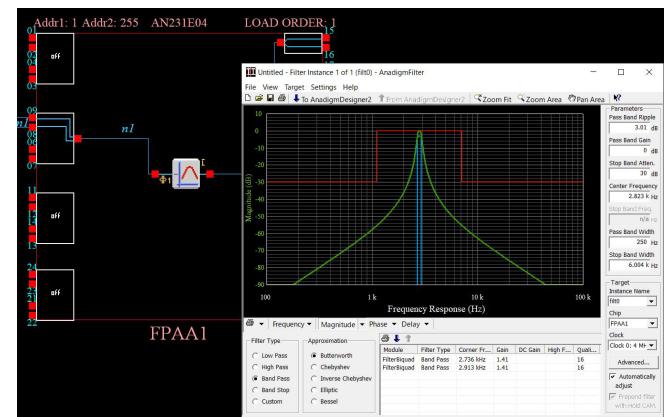

## Step5: AnadigmFilter で特性確認、及び調整

## 設計例3：ノッチ（50/60Hz ハム抑制）またはBPF（マイク帯域強調）

目的：電源ハムノイズの挿帯域除去。またはBPFで音色強調。

設計式（ノッチ中心）：

$$f_c \doteq \frac{1}{2\pi RC}$$

設計例 ( $f_0 \approx 50\text{Hz}$ ) :

•  $R = 33\text{k}\Omega$   $C = 100\text{nF} \rightarrow f_0 \doteq 48\text{Hz}$  (微調整必要)

実装ポイント：

- ノッチ深さは部品一致が支配的。FPAAn 使用なら可変素子で追い込み再構成が容易にできる。

- 受動ネットワーク後に低歪バッファを入れて負荷影響を遮断。

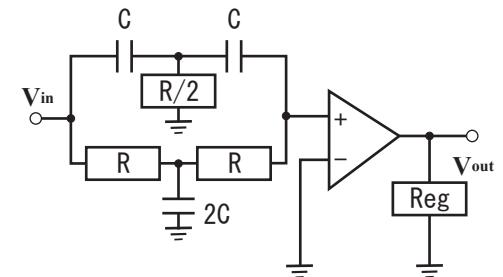

図：Twin Active notch filter 例

※：ここまで操作は Page-2 と同じ

Step5: AnadigmFilter で特性確認、及び調整

※：ページは機能を示したものであり、回路図、文章部、下部の図に相互互換性はありません。

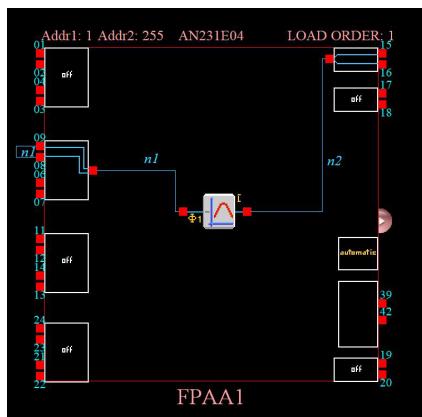

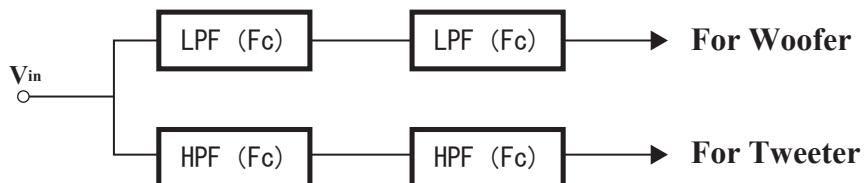

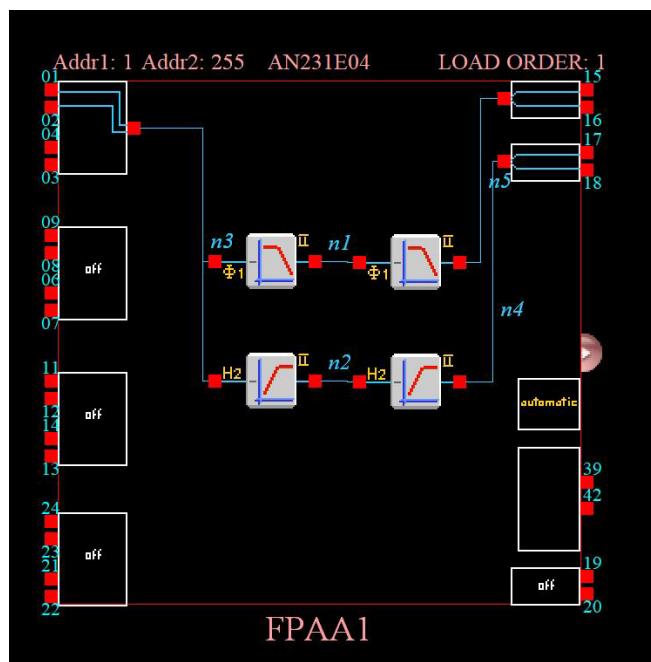

## 設計例 4 : アクティブ・クロスオーバー・フィルタ

目的：位相整合と平坦な合成特性、クロスポイントで -6db、合成でフラット

設計式（各段の  $F_c$  共通）：

2 次 LPF/HPF の各段をバターワースで設計して、直列で LR4 相当の特性を得る

設計例 ( $f_c \approx 2\text{kHz}$ ) :

- ・各段の LPF/HPF を同一条件で設計

- ・チャンネル間ゲインを後段のバッファで整合（感度差補正）

実装ポイント：

- ・FPAAs の内部配線で LPF/HPF のセルをコピー配置できる。 $F_c$  変更は R/C もしくはクロック基準の再構成で即応可能

- ・ツイーター / ウーファー間の遅延差はアライメントで補償（物理配置、ディレイセルの使用、またはディジタル側で補正）

- ・高次化に伴う位相周りは視聴と測定で最適化

図 : Active crossover 例

※: ここまで操作は Page-2 と同じ (Chip 内で接続可能)

※: ページは機能を示したものであり、回路図、文章部、下部の図に相互互換性はありません。