# 低消費電力フィールドプログラマブルアナログアレイを用いたワイヤレスセンシング

ブランドン・ランバーグ、デイビッド・W・グラハム

レーンコンピュータサイエンス・電気工学部門ウェストバージニア大学、モーガン

タウン、WV 26506

電子メール:brumberg@mix.wvu.edu, david.graham@mail.wvu.edu

**要約**—本稿では、無線環境におけるリソース制約アプリケーション向けのセンサーインターフェースおよび情報抽出用フィールドプログラマブルアナログアレイ (FPAAs) を提案する。低オーバーヘッドの再プログラミングと効率的な処理アーキテクチャにより、超低消費電力動作を実現した。温度センサー、心拍数アラーム、音声スペクトラム正規化器の合成を通じて再構成性と性能を実証し、それぞれ測定されたシステム全体の消費電力は、 $12.\mu\text{W}$ 、 $20.\mu\text{W}$ 、 $17.25\mu\text{W}$ であった。

## I. はじめに

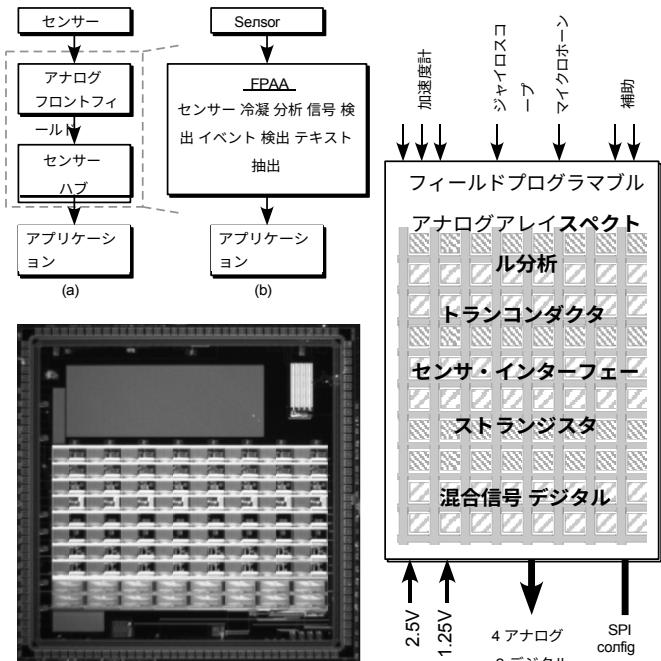

モバイルデバイスや無線センシングシステムにおけるセンサーの普及は、構成部品とエネルギー需要の増加によりアプリケーション開発を複雑化している。これらの無線デバイスでは、エネルギーはデバイス内に蓄積可能な量、あるいは環境から回収可能な量に制限される。図1(a)に示す「センサーハブ」概念に基づくシステムは、コンテキスト情報の抽出や低レベルなセンサータスク処理を専用ハードウェアで行うことで、アプリケーション設計を簡素化する。このようなシステムは、100Hz未満の帯域幅を持つ慣性センシングアプリケーションにおいて有効であることが実証されている。しかし、オーディオなど100Hzを超える信号帯域幅の場合、信号チェーン全体で低消費電力を維持することは依然として困難である。低消費電力の

特に電池駆動のデバイスでは、消費電力の低減がますます重要になっています。

リソース制約のあるセンシングアプリケーションの開発を容易にするため、図1(b)に示すアーキテクチャを提案する。このアーキテクチャでは、センシング指向のフィールドプログラマブルアナログアレイ (FPAAs) が、センサーインターフェースと情報抽出を効率的に実行する。FPAAsは、フィルタリングやセンサーインターフェースといった従来型アナログアプリケーションにFPGAの利点（例：迅速なプロトタイピング）をもたらす試みにおいて、注目を集めている[1]、[2]。さらに、トランジスタの複雑な大信号特性を活用し、信号処理や分類アルゴリズムをアナログ回路へ効率的にマッピングする研究も進められている[3]、[4]。

高速なセンサーインターフェース設計と低消費電力信号処理の融合可能性は、リソース制約のあるセンシングアプリケーションにおいてFPAAsを魅力的にする。しかし、高密度アナログパラメータ保存のコスト（揮発性記憶装置のリフレッシュに必要な高待機電力、あるいは不揮発性記憶装置への書き込みに伴う高インフラオーバーヘッド）が、低消費電力システム

における大規模FPAAsの適用を制限している。

本研究では、低消費電力センシング用途向けのFPAAsを提案する。低オーバーヘッドで高度に統合されたプログラミング

本研究は米国国立科学財団 (NSF) の助成金番号1148815の支援を受けて実施されました。

(c)

(c)

図1. (a) 従来のセンシングシステム。(b) センサーインターフェースおよび情報抽出プロックをFPAAで置き換えたセンシングシステム。

(c) 当社の $25\text{mm}^2$ FPAAダイの顕微鏡写真。(d) 当社のFPAA開発ボードのブロック図。当社のFPAAは $8 \times 10$ の演算ブロック配列で構成される：8つの同一チャンネルと10の機能特化ステージ。

アーキテクチャを開発した。その結果、FPAAにロードされる設計に応じて、再プログラミングに必要なエネルギーはわずか1~48mJであり、これにより本FPAAは低リソースシステムでの使用が可能となる。さらに、汎用アーキテクチャと比較して性能とリソース利用率を向上させるため、センシング用途に特化した信号経路アーキテクチャを設計した。

このFPAAは、状況認識や監視などの「持続的センシング」アプリケーションに適したフロントエンドである。これらのアプリケーションでは、システムは低レベルのデータ収集と処理を継続的に実行し、これらの低レベル操作に対しては時折のみ応答する。センサーインターフェース、信号解析、イベント検出などの低レベル操作の大部分をFPAAを用いて実装することで、システム設計を簡素化し、システム消費電力を低減できる。

本論文の全プロットは、標準的な $0.35\mu m$  CMOSプロセスで製造された $25mm^2$ のFPAA集積回路（図1(c)）からの測定値を示している。

## II. FPAAの設計

### A. 信号経路アーキテクチャ

FPAA内の回路基本要素（計算要素）は、一般的に構成可能なブロックの階層構造にグループ化される[5]、[6]。各ブロックは様々な計算要素を含み、異なるタイプのブロックが組み込まれる場合がある。従来のFPAAでは、最大3種類の固有ブロックタイプからなる汎用ブロックの均質配列が使用されてきた[6]、[7]。本FPAAでは、多様な演算要素（表I参照）を、センサーインターフェースおよび処理の各段階向けに、9種類の固有かつ機能特化型ブロックタイプに分類している。本FPAAはセンサー前処理とイベント検出を目的として設計されているため、図1(d)に示す並列化アーキテクチャを採用している。これは80個の演算ブロックを、8チャネル×10段階の信号フローに配置した構成である。信号分解は処理チェーンの初期段階で実行され、その後データは並列チャネルで処理されるため、残りの処理は低帯域幅かつ低電力で実行可能となる。

当社のFPAAのスイッチアーキテクチャは、FPGAで一般的なアイランド型アーキテクチャを本質的に採用している[8]。フルクロスバースイッチマトリクスがブロックレベルで演算素子の16端子を接続し、スイッチボックスが隣接ブロック間の6本の配線トラックを接続する。さらに各ステージ／チャネルには信号をグローバルに配線する長距離トラックが設けられている。全20,380個のスイッチは、ローカルSRAMビットで制御される伝送ゲートを用いて実装されている。

スイッチマトリクスによる寄生容量は、單一ブロック内の接続で203fF、隣接ブロックへの接続で400fFと測定された——これは[6]のフローティングゲート型FPAAと同等である。これらの寄生容量は顕著であり、信号経路にバッファなしの切り替え可能ネットを過剰に含めると性能が低下し、交流電力消費が増加する。

このような寄生要素の影響を低減するため、本FPAAには高粒度演算素子を導入し、信号経路内のスイッチ数を削減した。本FPAAの演算要素を表Iに示す。これらは多様な粒度と機能を持ち、性能と適用適性を向上させる。ほとんどの信号処理アプリケーションに適用可能で、オーディオ・振動アプリケーション向けに機能をステージ別にグループ化している。各グループを以下に説明する。

- 1) スペクトル解析：周波数分解アルゴリズムを合成するための、再構成可能なバイアス端子を備えたプログラマブルフィルター、エンベロープ検出器、OTAを含みます。

- 2) トランスクンダクタ： $G_m$  (TCA) ネットワークおよび判別関数を合成するための、様々な線形および非線形のトランスクンダクタンス要素を含みます。

$C$  ネットワークおよび判別関数を合成するための様々な線形および非線形のトランスクンダクタンス素子を含みます。

- 3) センサーインターフェース：オペアンプと抵抗器を備え、再構成可能なセンサーインターフェースを構築。

- 4) トランジスタ：専用要素として組み込むには特殊すぎる演算要素を合成するために使用される。

- 5) 混合信号回路：コンパレータ、S/H回路、プログラマブル幅パルス発生器などを含む。前段からの低速信号とのインターフェースで生じる短絡電流を無効化するため、電流不足状態かつ非重複プッシュプル論理で設計されている。

- 6) デジタル：フリップフロップとルックアップテーブルを含む。アナログ回路へのデジタル制御を追加し、アプリケーションプロセッサ向けのイベント検出およびデータレディ割り込みを生成するために使用される。合成レジスタの実行時書き込み/読み取りのためにFPAAのSPIピンに接続されている。

表I

計算要素

| 8つのBPF   | 56 OTA   | 8 インバータ        | 16 エンベロープ検出器  |

|----------|----------|----------------|---------------|

| 8 LPF    | 8 乗算器    | 32 コンパレータ      | 48個の電流源/電流シンク |

| 56 キャビシタ | 8 オペアンプ  | 8 バンプ回路        | 16パルス発生器      |

| 8個のPNP   | 16個の抵抗器  | 8 電圧-時間変換回路    | 16 非対称積分器     |

| 16 S/H   | 144個のFET | 32個のJKフリップフロップ | 16個の6入力2出力LUT |

### B. メモリプログラミングインフラストラクチャ

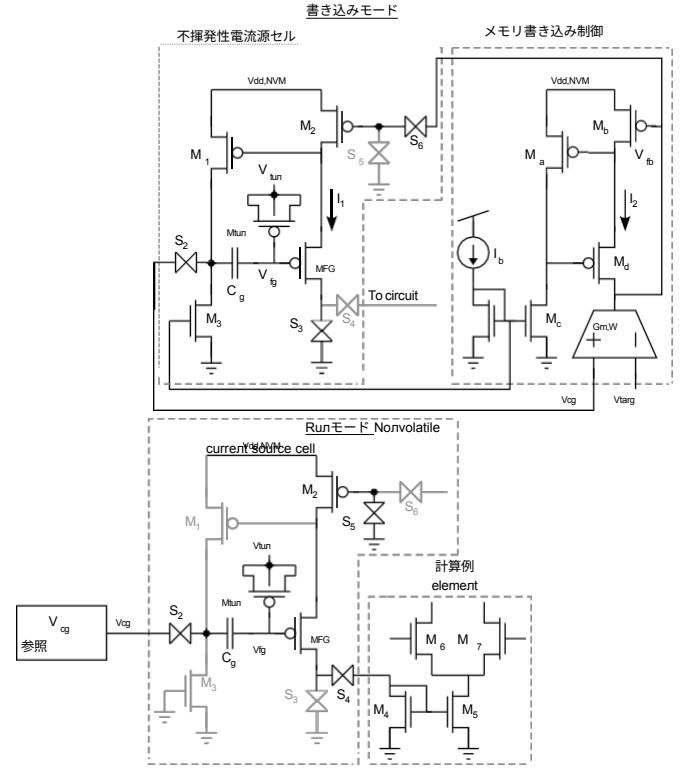

計算要素のプログラマブル特性（時定数、 $G_m$ 、パルス幅など）は、296個のアナログ不揮発性メモリ（NVM）要素によって制御されます。これらのメモリ要素は、フローティングゲートトランジスタをベースにしたプログラマブル電流源で構成されています。フローティングゲートトランジスタは、そのゲートに抵抗性接続を持たない。代わりに、「制御ゲート」がトランジスタの「フローティングゲート」に容量結合する。その結果、ファウラー・ノードハイム効果[9]やホットエレクトロン注入[10]によって変更可能な浮遊ゲート電荷が、制御ゲートから見ると、プログラム可能かつ不揮発性のしきい値電圧シフトを生み出す。

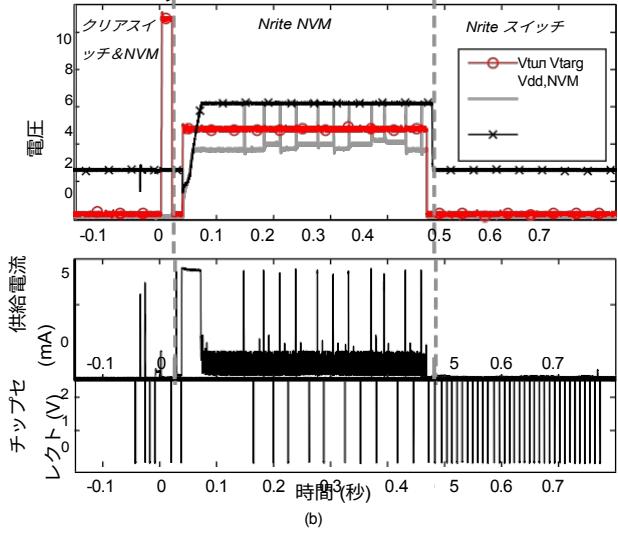

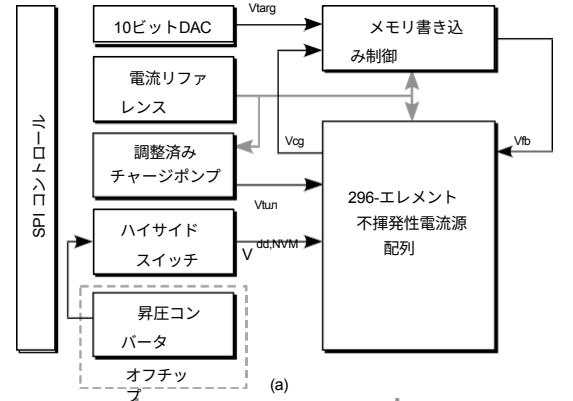

我々は、フローティングゲートにアナログ値を書き込むための高集積・省エネルギー最適化システム（図2(a)）を開発した。図3に詳細を示すNVM素子と書き込み制御回路は、[11]の連続時間プログラミング回路を基盤としている。再プログラミングプロセスを図2(b)に示すとともに、以下で説明する。

- 1) クリアスイッチ&NVM：まず、スイッチを制御するSRAMをクリアし、アナログ浮遊ゲートメモリをブロック消去することでFPAAをリセットする。ブロック消去は、 $V_{tun}$ に10.5Vパルスを印加し、全浮遊ゲートから電子をトンネル脱離させることで実施される。この電圧パルスはオンチップ高電圧チャージポンプで生成される。

- 2) 書き込みNVM：次に、アナログ値がNVMに書き込まれる。書き込みは、まず注入を容易にするためメモリ供給電圧 $V_{dd,NVM}$ を6Vまで上昇させ、その後個々の素子を順次書き込み制御回路に接続して $V_{targ}$ をNVMに保存することで実行される。 $V_{targ}$ は、オンチップDACによって各素子ごとに所望の値に設定される。書き込みプロセス中、オンチップ安定化チャージポンプを用いて $V_{tun}$ を4.5Vに設定し、 $M_{tun}$ を介した逆方向トンネル効果を回避する。

図2. (a) FPAAsのアナログ不揮発性メモリ(NVM)プログラミングシステムのブロック図。(b) FPAAsへの設計データロード過程の測定。FPAAs基板に流入する供給電流を測定。SPIチップセレクトピンはアプリケーションプロセッサからのデータ転送を示す。

3) 書き込みスイッチ：最終的にスイッチを設定し、配線を接続するFPAAsを所定の機能に配線する。我々は

ユーザー生成ネットリストをリストに変換するPCプログラム

プログラム対象スイッチ数

### C. FPAAsプログラミングの概要

アナログメモリへの書き込みはオンチップフィードバックループによって制御され、アプリケーションプロセッサからの唯一の関与はメモアドレスとDACコードワードを指定することです。その結果、我々は大幅に少ないオーバーヘッドしか発生させません

フィードバックループにプロセッサを必要とするシステム [6]。図2(b)の全プロセスで消費されたエネルギーは2.35mJであり、その33%は外部昇圧コンバータの起動時に消費される。この消費は、オンチップチャージポンプ（当社の $V_{tun}$ チャージポンプと同様）を用いて $V_{(dd,NVM)}$ を生成することで、ほぼ完全に排除できる。

図2(b)では、10個のNVMと33個のスイッチが書き込まれた。エネルギー内訳は、NVMあたり約0.12mJ、スイッチあたり $6.4\mu J$ 、再構成サイクルごとに定数の $0.94mJ$ である。これらのデータは、より大規模な負荷に対するエネルギー推定に使用される

図3. NVMセルの詳細。書き込みモードでは、フローティングゲートトランジスタ $M_{FG}$ を囲むローカルフィードバックループ( $M_{1,3}$ )が指数関数的注入特性を線形化する。NVMセルは個々に書き込み制御回路に接続され、この回路は $V_{fg}$ への注入電流を( $I_1$ )を変化させることで調整する。これにより $V_{fg}$ 上の電荷が $V_{cg} = V_{tun} + V_{targ}$ に一致させるまで制御される。調整されたカスケード電流ミラー、 $M_{(a-d)}$ は、メモリセル構造を複製し、 $I_1$ と $I_2$ 間の整合性を向上させる。実行モードでは、各NVMセルは電流源として対応する。

演算素子に接続される。

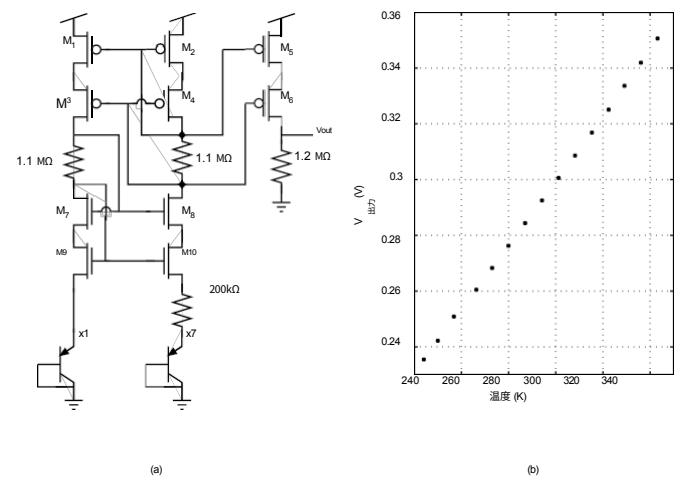

図4. (a) FPAAs内のデバイスを用いて合成した温度センサ。(b) 100K温度範囲における測定出力。

設計をFPAAsに組み込む際のエネルギーを推定するために使用される。例えば、図6の設計では478個のスイッチ、29ビットのLUT、52個のアナログNVMを使用し、総再構成エネルギーは10.42mJである。

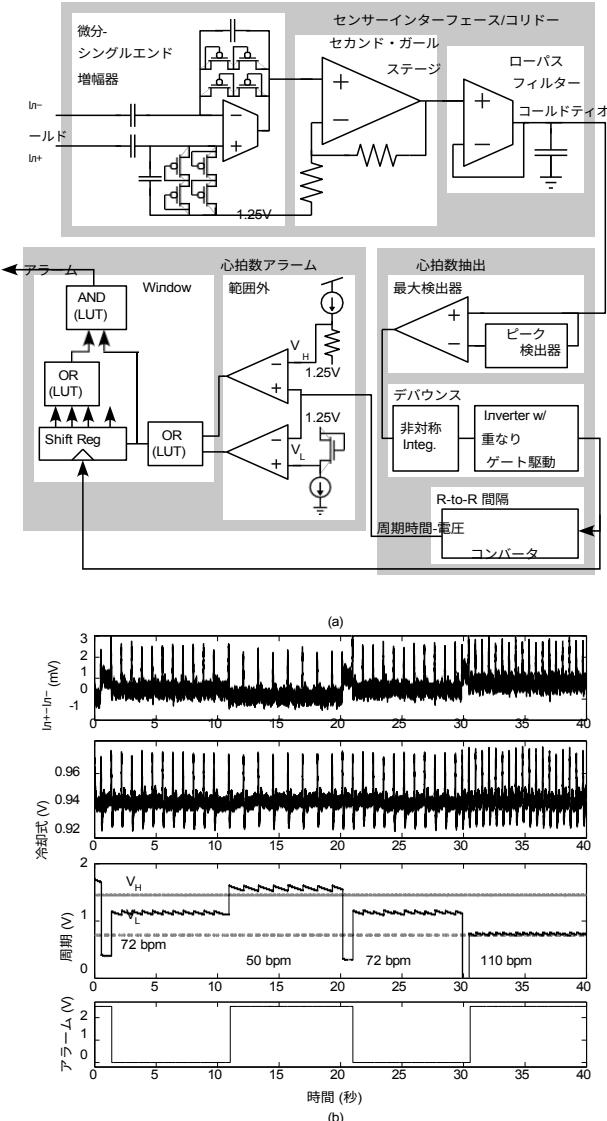

図5. (a) FPAで合成された心拍数モニタリングシステム。コンディショニングブロックを通して後、R波のピークでクロックされる時間-電圧変換器が周期を抽出する。周期はユーザー一定義の高/低しきい値と比較される。直近の2周期が安全範囲外の場合、警報が生成される。(b) 心拍数モニタリングシステムの測定応答。入力は心拍数変動に伴う2mV差動心臓信号と200mV 60Hzコモンモードノイズである。調整、抽出、警報サブシステムの出力をプロット。下段のプロットは範囲外心拍数の検出成功を示す。

### III. 実証実験

以下の実証実験は、無線センシングシナリオを代表する様々な応用においてFPAの有効性を検証する。全ての消費電力値(表II)は、FPAボード全体の供給電流(3V時)を測定して得られた。これらの値には出力バッファ、レギュレータ、リファレンスの電力も含まれており、従ってFPAを組み込みシステムに追加する際の電力コストを代表している。

**温度センサー**: FPAには、計算ブロックに組み込むには特殊すぎる回路を合成するためのデバイスレベルの要素が多数含まれています。温度センサーは...

表II

デモンストレーション結果

| 回路     | 動作電力          | ネット | NVM         | 構成エネルギー |

|--------|---------------|-----|-------------|---------|

| 温度センサー | 12 $\mu$ W    | 23  | 3(読み出しバッファ) | 1.97mJ  |

| 心拍数    | 20 $\mu$ W    | 55  | 18          | 5.52mJ  |

| オーディオ  | 17.25 $\mu$ W | 89  | 52          | 10.42mJ |

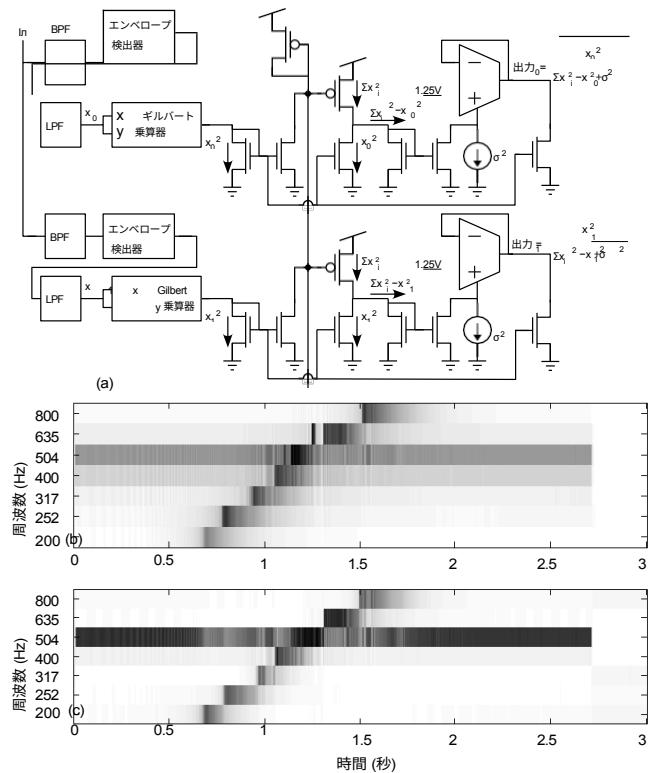

図6. (a) FPAで合成された音声スペクトル正規化システム。明瞭化のため7チャンネル中2チャンネルのみ表示。(b & c) 500Hzトーンとチャープの組み合わせに対するシステムの測定応答。(b) 正規化なし:  $x_t$ 。(c) 正規化あり:  $Out_t$ 。正規化により500Hzトーンの隣接帯域への漏れが低減され、その効果を確認できる。

図4(a)の温度センサは、デバイスレベルの素子のみで構成された回路の実証として合成された。BJTと抵抗の比率は1mV/Kの出力を得るために選択された。回路の測定された温度応答を図4(b)に示す。

**心拍モニター**: FPAは、センサーシステムの最初の3段階(センサーインターフェース、信号解析、イベント検出)の要件を満たすように設計された。これらの機能は、図5(a)に示す心拍モニタリングシステムの合成によって実証される。差動増幅器は[12]に基づき、システムのバックエンドは[13]に着想を得ている。各記号は、ソフトレジスタ(フリップフロップの集合体)を除き、単一の演算要素(表I参照)に直接対応する。FPAの混合粒度構造により、この比較的大きなシステムが少数の要素にマッピングされた。

**音声スペクトル正規化**: FPAAのアーキテクチャは、アナログフィルタバンクを用いた音声・振動信号処理に適している。フィルタチャネルの情報は高度に相関しており、分類準備のため後続処理が必要となる。図6では、FPAAで合成された[14]の非相関化アルゴリズムの回路実装を示す。このアルゴリズムの並列チャネルに対する非線形抑制は、アナログ回路へ効率的にマッピングされる。この回路はフィルタバンクの周波数応答を鋭敏化し、チャンネルを正規化することで分類用の尺度不变特徴を生成する。消費電力は $17.25\mu\text{W}$ である。比較のため、[3]では同等のフィルタバンクアルゴリズムの単一チャンネルをFPAAで実装した例が記載されており、その消費電力は $34.5\mu\text{W}$ であった。

#### IV. 結論

FPAAの代表的な応用例としてセンサーインターフェースが挙げられる。無線接続センサーモノのインターネット(IoT)の応用が拡大する中、センサーデバイスの数は増加する一方、デバイス当たりの消費電力削減が求められる。この観点から、我々は厳しい電力制約下にあるシステム向けに、大規模かつ低オーバーヘッドのFPAAを開発した。

大規模信号処理システムの合成を容易にするため、計算要素と並列信号フロー構造を組み合わせたFPAAを設計した。図6に示すシステムは52個のアナログパラメータと89個のネットを有する(合成されたチャネル読み出しきゃなは図示せず)。これは再構成可能なアナログファブリックで実装された、公表済みの最大規模のシステムの一つである。

#### 謝辞

FPAAのレイアウト作成において、Brandon Kelly氏およびSpencer Clites氏にご協力いただきましたことに感謝申し上げます。

#### 参考文献

- [1] D. アンダーソン、C. マークジャン、D. バーシュ、H. アンダーソン、P. フー、O. パルシンスキ、

D. Gettman、I. Macbeth、および A. Bratt、「フィールドプログラマブルアナログアレイとその応用」、*IEEE カスタム集積回路会議議事録*、カリフォルニア州サンタクララ、1997年5月、555~558ページ。

- [2] B. Pankiewicz、M. Wojcikowski、S. Szczepanski、および Y. Sun、「CMOS 連続時間OTA-C フィルタ用途向けのフィールドプログラマブルアナログアレイ」、*IEEE Journal of Solid-State Circuits*、第37巻、第2号、125~136ページ、2002年2月。

- [3] A. Basu、S. Brink、C. Schlottmann、S. Ramakrishnan、C. Petre、S. Kozioł、

F. Baskaya、C. Twigg、P. Hasler、「フローティングゲートベースのフィールドプログラマブルアナログアレイ」、*IEEE Journal of Solid-State Circuits*、vol. 45、no. 9、pp. 904~922、2010年9月。

- [4] D. Fernández、L. Martínez-Alvarado、および J. Madrenas、「標準 CMOS テクノロジーによるトランシリニア、対数領域 FPAA」、*IEEE Journal of Solid-State Circuits*、第47巻、第2号、490~503ページ、2012年2月。

- [5] R. Wunderlich、F. Adil、P. Hasler、「フローティングゲートベースのフィールドプログラマブル混合信号アレイ」、*IEEE Transactions on Very Large Scale Integration (VLSI) Systems*、vol. 21、no. 8、pp. 1496~1505、2013年8月。

- [6] C. Schlottmann、S. Shapero、S. Nease、and P. Hasler、「低消費電力信号処理のためのデジタル強化型動的再構成可能アナログプラットフォーム」、*IEEE Journal of Solid-State Circuits*、vol. 47、no. 9、pp. 2174~2184、Sept. 2012.

- [7] S. Peng、G. Gurun、C. Twigg、M. Qureshi、A. Basu、S. Brink、P. Hasler、および F. Degertekin、「大規模再構成可能スマートセンサーチップ」、*IEEE International Symposium on Circuits and Systems*、台湾、台北、2009年5月、2145~2148ページ。

- [8] I. Kuon、R. Tessier、J. Rose、「FPGA アーキテクチャ：調査と課題」、*Foundations and Trends in Electronic Design Automation*、第2巻、第2号、135~253ページ、2008年2月。

- [9] M. Lenzlinger and E. Snow、「熱成長SiO<sub>2</sub>へのファウラー・ノルドハイムトンネル効果」、*Journal of Applied Physics*、vol. 40、no. 1、pp. 278~283、1969年9月。

- [10] P. Hasler、A. Andreou、C. Diorio、B. Minch、and C. Mead、「ボルツマン輸送から一貫して導出される衝撃イオン化と高温電子注入」、*VLSI Design*、vol. 8、no. 1~4、pp. 454~461、1998年5月。

- [11] B. Rumberg and D. Graham、「連続時間プログラミング用フローティングゲートメモリセル」、*IEEE Midwest Symposium on Circuits and Systems 論文集*、Boise, ID、2012年8月、pp. 214~217。

- [12] R. Harrison and C. Charles、「神経記録用途向け低消費電力・低雑音CMOS増幅器」、*IEEE Journal of Solid-State Circuits*、vol. 38、no. 6、pp. 958~965、2003年6月。

- [13] H. Abdalla and T. Horiuchi、「アナログVLSI低消費電力エンベロープ周期性検出器」、*IEEE Transactions on Circuits and Systems I, Regular Papers*、vol. 52、no. 9、pp. 1709~1720、2005年9月。

- [14] O. Schwartz and E. Simoncelli、「自然信号統計と感觉利得制御」、*Nature Neuroscience*、vol. 4、pp. 819~825、Aug. 2001.