## マシンビジョンシステム用FPGAアクセラレータ

**要約。**本論文は、画像前処理のためのFPGAタイプのプログラム可能アクセラレータの提案について述べる。アクセラレータの構造は、CPLDデジタル回路に基づいてモデル化されている。ここでの革新点は、電流モードを使用していることで、これにより、ナノメートル技術でアクセラレータを実装することが可能になる。本論文で提案されているもう一つの独創的な解決策は、再構成可能な多出力電流ミラーである。本論文では、ハードウェア層とそのプログラミング方法について述べる。RGB-YCrCbカラースペース変換器の実装例を紹介する。さらに、レイアウト後のシミュレーションで得られた物理的パラメータも提示する。このソリューションは、スタンドアロンのプログラマブル回路として、あるいはより大規模なアナログ・デジタルシステムのIPコアとして利用することができます。(視覚システム用FPGAアクセラレータ)

**要約。**本論文では、画像の前処理用プログラマブルFPGAアクセラレータの提案について述べる。アクセラレータの構造は、CPLDデジタル回路をモデルとしている。その革新性は、電流モードを利用することで、ナノメートル技術でのアクセラレータの実装を可能にした点にある。本論文で提案されたもう一つの独創的なソリューションは、再構成可能な多出力電流ミラーである。本論文では、ハードウェア層とそのプログラミング手法について論じている。アクセラレータにおけるRGBからYCrCbへの色空間変換器の実装を紹介し、ポストレイアウトシミュレーションで得られた物理的パラメータを提示しています。このソリューションは、独立したプログラマブル回路、あるいはより大規模なアナログ・デジタルシステムのIPコアとして利用することができます。(視覚システム用FPGAアクセラレータ)

**キーワード：**再構成可能回路、色空間変換器、ハードウェアアクセラレーション、ビジョンシステム、FPGA、RGB、YCrCb。

**キーワード：**再構成可能回路、色空間変換器、ハードウェアアクセラレーション、視覚システム、FPGA、RGB、YCrCb。

### はじめに

デジタル回路市場は、1980年代にFPGA型再構成可能回路の導入により革命的な変化を遂げた。そのアナログ版である、電圧モードで動作するいわゆるFPAAsの実装が、現在文献で登場している[1-5]。しかし、エレクトロニクスの小型化の傾向により、既存のFPAAsアーキテクチャを現代のナノメートル技術で実装することは不可能であり、そのため、多くの場合、ビジョンシステムなどのより大規模なアナログデジタルシステムへの応用が妨げられています。著者らは、電流モードで動作し、標準的なCMOSナノメートル技術で実装可能なFPAAsアーキテクチャを提案することにしました。SI(スイッチ電流)などの電流技術は、その精度レベルから主に画像処理タスクに用いられていることは特筆すべきである。これらの技術に共通するのは低消費電力であり、これによりSIプロセッサをスタンドアロンの小型システムに適合させることができます。

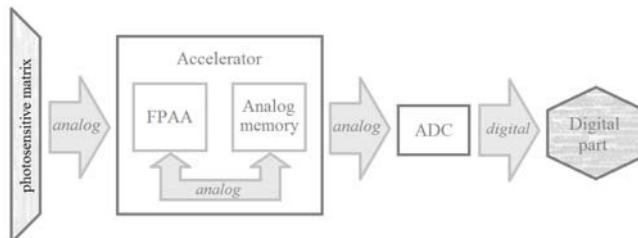

図1. FPGAアクセラレータに基づくイメージセンサー

図1は、感光性マトリクスを使用したセンサーの実装にアクセラレータを適応させる可能性を示しています。本論文で提案するアクセラレータは、マトリクスから得られる様々な画像処理アルゴリズムの実装に使用できます。迅速なプログラミングが可能であるため、アナログバッファに保存された画像に対して、以下のタスクを実行できます。

メモリ [6]。第2章では、再構成可能な電流などの基本的な再プログラム可能モジュールの構造について説明します。

ミラー。第3章では、電流モードで動作し、プログラマブルルーティングを介して接続されたセルで構成されるアクセラレータのアーキテクチャについて説明します。第4章では、アクセラレータに実装されたRGB-YCrCbカラースペースコンバータの例を紹介します。

### 再構成可能な電流ミラー

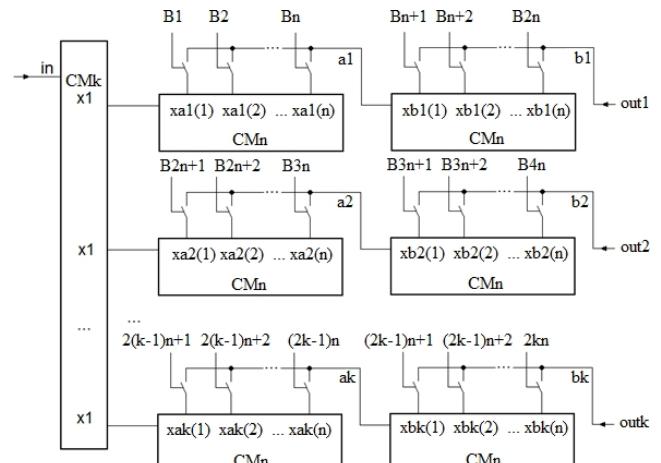

アクセラレータの基本的な再構成可能要素は、図2に示す多出力プログラマブル電流ミラーです。

図2. プログラマブル電流ミラー

これはアナログ-デジタルインターフェースを備えている。アナログ入力は、単位スケーリング係数を持つ  $k$  出力ミラー  $CM_k$  によって複製される。次に、処理ラインは、 $n$ ビットコードワードによって制御される  $n$ 出力電流ミラー  $CM_n$  に基づくアーキテクチャのD/Aコンバータのペアで構成される列を備えています。このようなコンバータの構造は、文献[7]で紹介されています。コンバータのペアは  $2n$ ビットワードによって構成され、特定のペアの出力における信号  $out_i$  は、 $a_i, b_i$  の値を持ちます。

$in_i$ 、ここで  $a_i$  および  $b_i$  は  $CM_n$  コンバータの要約スケーリング係数である。D/Aコンバータのトランジスタサイズは、係数の許容値の範囲を定義する式(1)を満たすように、Hooke-Jeeves法[8]を用いて計算されている。

$$(1) \quad \alpha_i = a_i \cdot b_i, \quad \alpha_i \in \{0.02, \dots, 4.2\}$$

、

特筆すべきは、信号処理ライン（アナログインターフェースレベルから）のミラー数が奇数であるため、図2の回路が単一の電流ミラーとして動作することである。 $2kn$ ビットはデジタルを構成する。

インターフェースであり、 $k$ 個の出力のうちの1つのスケーリング係数の値を決定するために使用されます。また、選択されたスケーリング係数 $a_i$ を、係數 $a_i$ と $b_i$ の組み合わせを最低2つ使用して実装できることも特筆すべき点です。

( $a_i \cdot b_i$  に等しい最大スケーリング係数は除く)。再構成可能なミラーに実装できる固有のスケーリング係数の数は、以下の通りである。

$$2^n - 1$$

$$(2) \quad 2^{2n} - \sum_{i=1}^{2^n-1} i$$

残りの係数は冗長である。冗長性は欠点ではなく、この実装の利点である。なぜなら、冗長性のおかげで、より低い誤差で所定のスケーリング係数を反映するBベクトルのビット組み合わせを選択できるからである。ビットベクトルの選択は、以前に生成された冗長解のグリッドに基づいて行われる。このグリッドは、ミラーの出力における正の電流  $outp$  および負の電流  $outm$  のすべての組み合わせについて、ダイオード接続の相補トランジスタペアを搭載したミラーのレイアウト後シミュレーションに基づいて計算されます。このグリッドに基づいて、単一のビットの組み合わせに対するスケーリング係数の割り当てが定義されています。

$$(3) \quad B_j \leftarrow \frac{outp_j - outm_j}{2 \cdot |in|}, \quad j \in \{1, 2, 3, \dots, 2^{2n}\}$$

ここで、 $in$  は両方のケースで入力電流です。与えられた  $B_j$  ベクトルの選択基準は、スケーリング係数の反射誤差が最も小さいことです。表 1 は、図 2 のミラーの 8 出力実装のレイアウト後のパラメータを示しています。

図2. 範囲(1)内の任意のスケーリング係数は、誤差が2.24%以下で実装可能である。

表 1. 再構成可能な電流ミラーのパラメータ

| パラメータ   |                   | 値                     |

|---------|-------------------|-----------------------|

| アーキテクチャ | 技術 / 電源           | 180 nm / 1.8 V        |

|         | 出力数 (k)           | 8                     |

|         | プログラミングビット数 (2kn) | 96                    |

|         | 固有のスケーリング係数の数     | 2080                  |

| レイアウト   | 表面積               | 21500 $\mu\text{m}^2$ |

|         | 消費電力              | 2.29 mW               |

|         | 最大周波数             | 12 MS/s               |

|         | 入力および出力信号の範囲      | 0~10 $\mu\text{A}$    |

|         | スケーリング係数の範囲       | 0.02 – 4.1986         |

|         | 最大係数誤差            | 2.24                  |

|         | 平均係数誤差            | 0.0657%               |

### プログラマブルアレイ

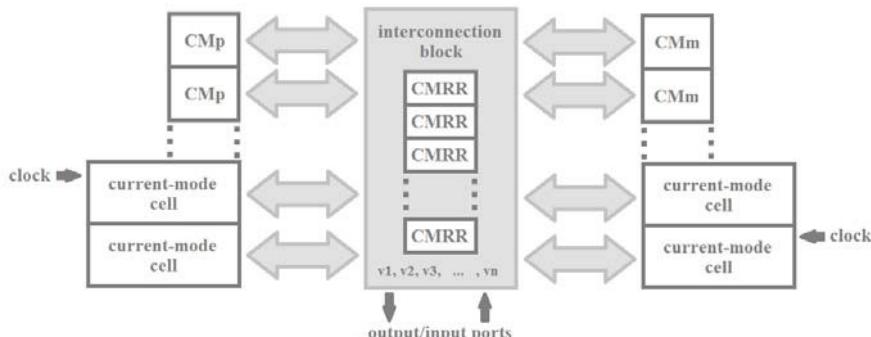

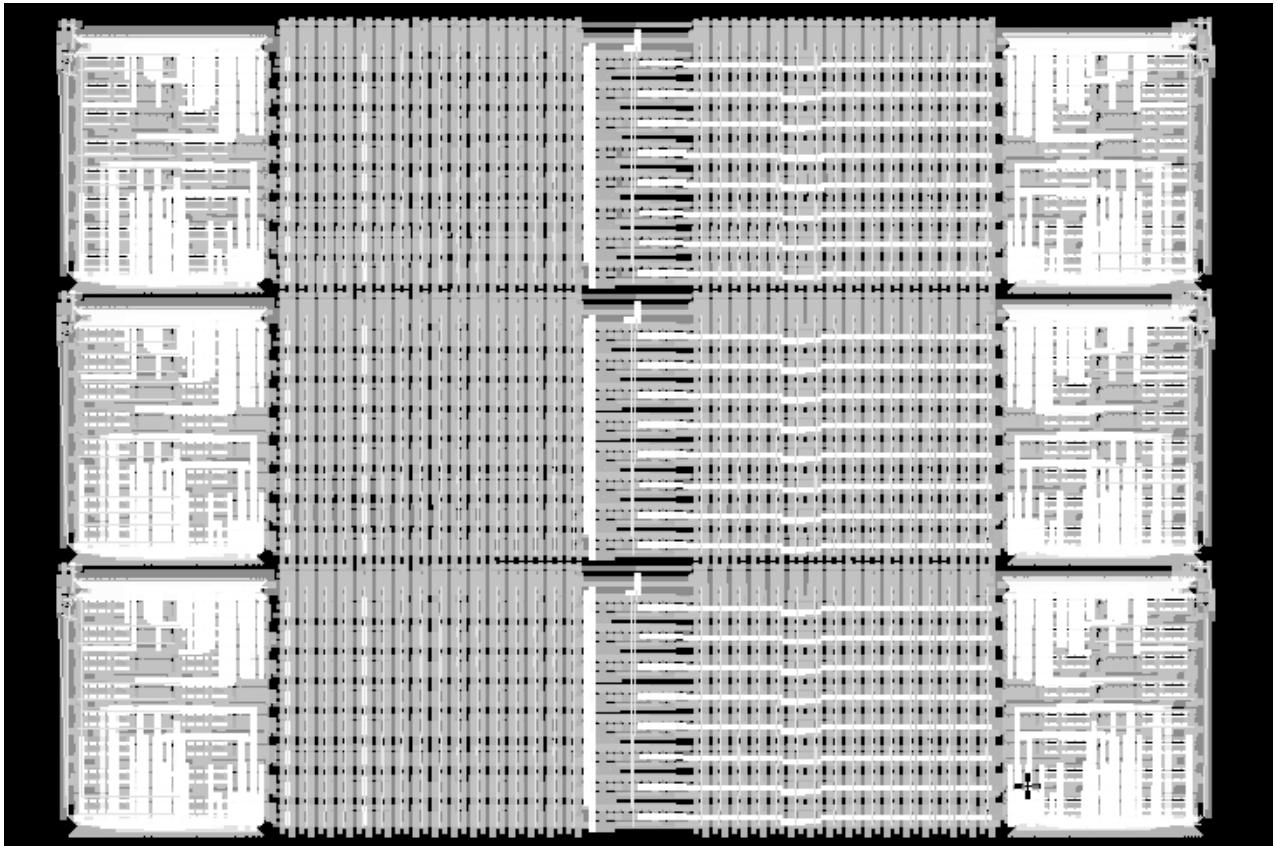

図3. プログラマブルアレイのレイアウト

提案された FPAK アクセラレータのアーキテクチャは、CPLD デジタル回路に基づいています。アクセラレータの簡略化されたレイアウトを図 3 に示します。回路の中心となるのは、いわゆるグローバル相互接続マトリックスです。このブロックには、デジタルでプログラム可能なノード  $v_i$  が含まれており、キーを介して、電流モードセルからの入力信号および出力信号、ならびに入力ポートおよび出力ポートを接続することができます。プログラム可能なキーは、一对の相補 CMOS トランジスタで実装されています。アクセラレータは、平衡構造として動作します。ルーティングブロックに追加されたセルの対称的な応答を確保するため、文献[10]で提示されているコモンモード除去比 (CMRR) [9]回路が使用されている。これは、接続ブロックと電流セル間のデータ転送における中間ステップを構成する。また、規則 (4) に従って、否定されない応答  $p$  および否定される応答  $m$  のノードを選択することにより、動作の対称性も確保されている。

$$\{p_i, m_i\} \leftarrow \{v_{\frac{n}{2}+l-i}, v_{\frac{n}{2}+i}\}, \quad i \in \{1, 2, 3, \dots, n\}$$

ここで、 $n$  はアクセラレータで使用可能なノード数である。完全な回路は、プログラマブル 集積 回路 として実装でき、セル で構成される。

第 2 章で説明した再構成可能なミラー、積分器、メモリ、その他の電流セル、あるいは、より大規模なアナログ-デジタルシステムのトポグラフィーの一部である、いわゆる IP コアとして。次の章では、3 組の再構成可能なミラーで構成される IP コアとしての回路の使用について紹介します。

### RGBからYCrCbへの変換器

感光マトリクスはアナログ形式で信号を提供するため、アナログ回路を使用した画像前処理を実装することは費用対効果が高く[11]、ビジョンシステムの複雑さを軽減します[12, 13]。感光マトリクスからの画像に対して行われる基本的な操作の1つは、輝度成分と色差成分で記述されるYCrCb空間への変換です[6]。従来の RGB 表現は、人間の目が画像を認識する方法を反映しません。

光の変化に対して色よりも敏感である。したがって、従来の表現を使用することは、以下の理由から非効率的である。

情報冗長性 [14] へ。YCrCb 空間への変換は、輝度情報を使用して表現できる画像処理において、より幅広い可能性をもたらします

高解像度データおよび色差に関する圧縮データを使用して保存される。RGB 空間から YCrCb 空間への変換は、式(4)で表される。

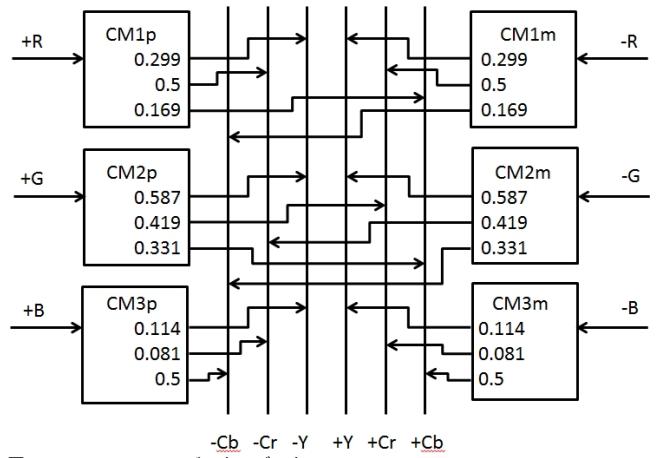

$$(4) \begin{bmatrix} \pm Y \\ \pm Cr \\ \pm Cb \end{bmatrix} = \begin{bmatrix} 0.299 & 0.587 & 0.114 \\ 0.5 & -0.419 & 0.081 \\ -0.169 & -0.331 & 0.5 \end{bmatrix} \begin{bmatrix} +Y \\ +Cr \\ +Cb \end{bmatrix}$$

現在の技術では、上記の変換は、係数行列の列に対応するスケーリング係数を持つ3出力電流ミラーを使用して実装されています。加算演算は、キルヒホッフの電流法則に従ってノードで行われます。図4は、上記の変換を実装する、平衡構造で動作するミラーの接続レイアウトを示しています。係数の負の値は、入力ノードを対称的に置換することで得られる。図5は、第3章で説明したサンプルIPコアアーキテクチャのレイアウトを示している。表2は、サンプル入力の組み合わせについて、回路の応答と理論値との比較を示している。IPコアの消費電力は13.86 mWである。回路の動作速度は4 MS/sである。

図4. RGB->YCrCbコンバータのデータフロー

図5. 3組の8出力電流ミラー、32ノードの配線、中央にCMRRコアを備えたRGB→YCrCbコンバータ用IPコアのレイアウト

表2. RGB->YCrCb コンバータの応答

| 入力RGB<br>[μA] | YCrCb (式(3)より)<br>[μA] | レイアウト後シミュレーションによる<br>YCrCb<br>[μA] |

|---------------|------------------------|------------------------------------|

| 2             | 2                      | 1.943                              |

| 2             | 0.324                  | 0.315                              |

| 2             | 0                      | 0.041                              |

#### 要約

本論文は、ビジョンセンサー用のハードウェアプログラマブルアクセラレータの提案について述べる。これは、現代のナノメートル技術におけるFPGA型ソリューションの適応に関する問題への答えである。この回路は、その構造が変更しやすいという点でも有用である。したがって、スタンドアロンの集積回路として、また

より大規模なシステムのトポグラフィーの構成要素としても使用できます。本アクセラレータにおけるカラースペースコンバータの実装例は、センサー技術におけるその応用可能性を示しています。画像変換時間は、QVGA規格で19.2ミリ秒、HVGAで38.4ミリ秒、VGAで76.8ミリ秒です。

#### 参考文献

- [1] Brink S.、Hasler J.、Wunderlich R.、「Adaptive Floating-Gate Circuit Enabled Large-Scale FPAAs」、Very Large Scale Integration (VLSI) Systems、IEEE Transactions on、vol. 22、第11号、2307-2315頁、2014年

- [2] Schlottman C.R.、Petre C.、Hasler P.E.、「FPGA構成のための高レベルSimulinkベースツール」、Very Large Scale Integration (VLSI) Systems、IEEE Transactions on、Vol. 20、

- ベースの FPAAs 構成ツール、超大規模集積回路 (VLSI) システム、*IEEE* トランザクション、第 20 卷、第 1 号、10-18、2012

- [3] Nease S., George S., Hasler P., Koziol S., Brink S., 再構成可能なアナログプラットフォーム上の電圧モード CMOS 樹状突起のモデリングと実装、*IEEE Transactions on Biomedical Circuits and Systems*、Volume: 6, Issue: 1, 76-84、2012

- [4] Pankiewicz B., Wojcikowski M., Szczepanski S., Yichuang S., CMOS 連続時間 OTA-C フィルタアプリケーションのためのフィールドプログラマブルアナログアレイ、*Journal of Solid-State Circuits*、vol. 37, no 2, 2002

- [5] Kutuk H. and Kang S.M., A field-programmable analog array (FPAAs) using switched-capacitor technique, in *Proc. IEEE Int. Symp. Circuits and Systems*, vol. 4, 41-43, May 1996

- [6] Handkiewicz A., Mixed-Signal Systems: A Guide to CMOS Circuit Design, John Wiley and Sons, 2002

- [7] Naumowicz M., Szczęsny Sz., Handkiewicz A., 「6ビット低電力D/Aコンバータ（スイッチング電流技術）」、*Elektronika: konstrukcje, technologie, zastosowania*、134-136, No. 9, 2013

- [8] Hooke R., Jeeves T.A., 数値および統計的問題の「直接探索」による解法、*J. Assoc. Comp.*、8(2), 212-229, 1961

- [9] Giustolisi G., Palmisano G., Palumbo G., CMOS オペアンプの CMRR 周波数応答、*IEEE Transactions on Instrumentation and Measurement*、vol. 49, no. 1, 2000

- [10] Śniatała P., Handkiewicz A., Naumowicz M., Szczęsny Sz., Melosik M., Katarzyński P., Kropidłowski M., 新しいコンバータ構造を備えたスイッチング電流シグマデルタ変調器

- VHDL-AMS 記述に基づく設計、*International Journal of Electronics and Telecommunications*、391-396, vol. 59, issue 4, 2013

- [11] Vittoz E., Analogue VLSI signal processing: Why, where and how, *Analog Integr. Circ.* S. 6, 27-44, 1994

- [12] Ahirwal B., Khadare M., Mehta R., RGB から YIQ および YCbCr への色空間変換のための FPGA ベースのシステム、*Proc. Int. Conf. on Intelligent and Advanced Systems*, 1345-1349, クアラルンプール、2007

- [13] Li S.-A., Chen C.-Y., Chen C.-H., 色空間変換のためのシフト・アンド・アドベースのハードウェアアクセラレータの設計、*J. Real-Time Image Proc.* <http://dx.doi.org/10.1007/s11554-013-0324-7>, 1999

- [14] Kim K. and In-Cheol P., Combined image signal processing for CMOS image sensors, *IEEE Symp. on Circuits and Systems*, 3185-3188, Island of Kos, 2006

-

- 著者 :** Ph. D. Szymon Szczęsny, ポズナン工科大学、コンピューティング学部, Piotrowo 3A, 60-965 ポズナン, E-mail : [szymon.szczesny@put.poznan.pl](mailto:szymon.szczesny@put.poznan.pl); prof. Andrzej Handkiewicz (Ph. D.), ポズナン工科大学、コンピューティング学部, Piotrowo 3A, 60-965 ポズナン, E-mail : [Andrzej.Handkiewicz@put.poznan.pl](mailto:Andrzej.Handkiewicz@put.poznan.pl); M. Sc. Mariusz Naumowicz, ポズナン工科大学、コンピューティング学部, Piotrowo 3A, 60-965 ポズナン, M. Sc. Michał Melosik, ポズナン工科大学、コンピューティング学部, Piotrowo 3A, 60-965 ポズナン, E-mail: [michał.melosik@put.poznan.pl](mailto:michał.melosik@put.poznan.pl)。