本出版物の議論、統計、著者プロフィールは以下でご覧いただけます：<https://www.researchgate.net/publication/272355958>

## 新規CCIIベースのフィールドプログラマブルアナログアレイとその6次バターワース

### LPFへの応用

Radioengineering誌掲載論文 · 2013年6月

引用文献

7

閲覧数

42

著者2名 (内訳：

Soliman A. Mahmoud シャルジャ大学

208 出版物 1,572 引用

プロフィールを見る

本出版物の著者の中には、以下の関連プロジェクトにも携わっている者がいます：

CMOS フィールドプログラマブルアナログアレイの設計とその応用 [プロジェクトを見る](#)

脳波検出システム [プロジェクトを見る](#)

ユーザーはダウンロードしたファイルの機能強化を要求しています。

# 新規CCIIベースのフィールドプログラマブルアナログアレイ とその6次バターワースLPFへの応用

Soliman MAHMOUD<sup>1,2</sup>, Eman SOLIMAN<sup>3</sup>

<sup>(1)</sup> 電気・コンピュータ工学科、シャルジヤ大学、27272、シャルジヤ、UAE

<sup>2</sup> ファイユーム大学 電気工学科、ファイユーム、エジプト

<sup>3</sup> カイロ・ジャーマン大学 (GUC) 電気電子工学科、エジプト・カイロsolimanm@sharjah.ac.ae, eman.azab@guc.edu.eg

**要旨.** 本論文では、フィールドプログラマブルアナログアレイ (FPAA) を提案する。提案するFPAAは、7つの構成可能アナログブロック (CAB) が六角格子状に配置され、CAB同士が直接接続される構造を有する。この構造により、信号経路の寄生容量が低減され、チップ全体の周波数応答が改善される。FPAAのCABは、新規開発の完全差動型デジタルプログラマブル電流コンベア (DPCCII) を基盤とする。DPCCIIのプログラマビリティは、デジタル制御の3ビットMOSラダー電流分割ネットワークにより実現される。特定のアナログ制御電圧信号を生成するために追加のバイアス回路は不要である。DPCCIIは、全プログラミング範囲において定常待機電力消費、オフセット電圧、帯域幅、高調波歪みが一定である。提案するFPAA上に、WLAN/WiMAX受信機に適した6次バターワース可変LPFを実装した。フィルタの消費電力は1V電源で5.4mW、遮断周波数は5.2MHzから16.9MHzまで調整可能である。全ての回路はTSMCの90nm CMOS技術を用いてシミュレーションを実施し、Cadenceを用いて解析を行った。

## キーワード

電流分割ネットワーク、デジタルプログラマブル電流コンベア、フィールドプログラマブルアナログアレイ、調整可能なWLAN/WiMAX レシーバ。

## 1. はじめに

フィールドプログラマブルアナログアレイ (FPAA) は、アナログ回路の設計検証に使用される再構成可能なハードウェアプラットフォームである。FPAAチップは、連続時間フィルタ、可変利得増幅器、発振器など、様々なアナログ回路を実現するために使用できる[1]。FPAAは、相互接続された構成可能アナログブロック (CAB) の配列である。CABは、電圧オペアンプ[2]、オペアンプ型トランコンダクタンス増幅器 (OTA) [1]、電流コンベア (CC) [3]などのアナログ能動回路を用いて実装される。これらの回路は、プログラマブル特性または定数特性で設計可能である。CABは以下を用いて相互接続される

相互接続ネットワークにより、電圧信号と電流信号がチップ内部でCAB間を伝搬可能となる[1-4]。FPAAはWLAN/WiMAXのようなマルチスタンダード受信機を実現する理想的な候補である。これはチップが可変仕様のフィルタと増幅器を実現できることに起因する。ただし、受信機の直線性と消費電力は、FPAA内部で使用される基本能動回路にのみ依存する。

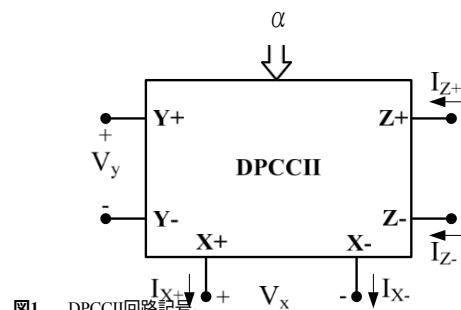

電流コンベア (CC) はFPAAの優れた候補アクティブ回路である。CCは[5-6]で導入され、高周波電圧モード応用に適している。第二世代電流コンベア (CCII) はY、X、Zと名付けられた三端子アクティブ回路である。CCIIではY-X端子間とX-Z端子間にそれぞれ単位利得の電圧モード増幅器と電流モード増幅器が実現される。[7-8]では、X端子とZ端子間にデジタル制御可能なプログラマブル電流係数を導入することで、CCIIのプログラマブル版が提案された。DPCCIIの回路記号を図1に示す。その端子特性は式(1)で与えられる。

$$\begin{bmatrix} I_y \\ I_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ \alpha & 0 & 1 \end{bmatrix} \begin{bmatrix} V_y \\ V_x \\ V_z \end{bmatrix} \quad (1)$$

ここで $\alpha$  ( $0 \leq \alpha \leq 1$ ) はデジタルでプログラム可能な利得係数である。

図1. DPCCII回路記号。

文献[8]のDPCCII回路は、CMOS電流分割ネットワーク (CDN) を用いてXとZ間の電流を制御した。しかしながら、使用されたCDNでは、全ての回路トランジスタが飽和状態にあることを保証するために可変バイアス電圧を生成する追加回路が必要であり、この特徴により提案するFPAAのハードウェア複雑度が大幅に低減される。

本論文では、外部バイアス回路を必要としない異なるCDNを用いた、提案するFPAAのハードウェア複雑性を大幅に低減する新規な完全差動DPCCIIの実現法を示す。

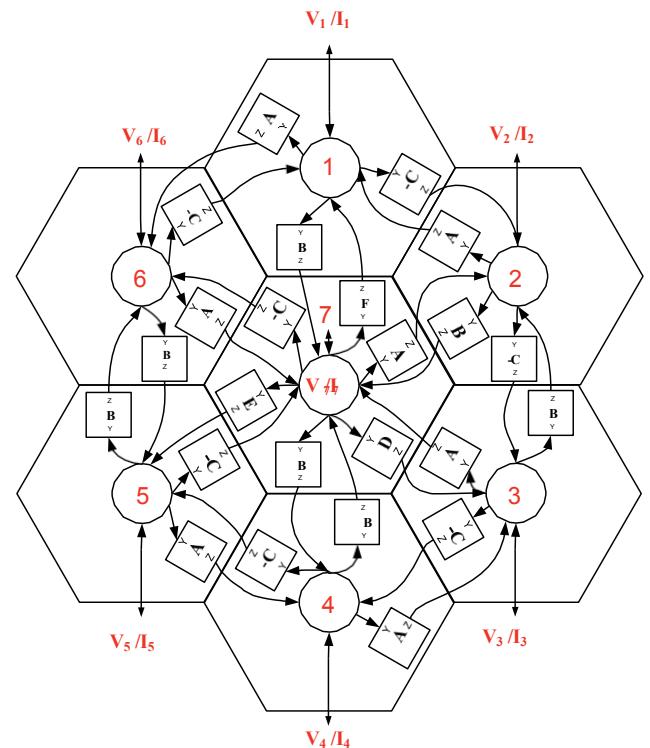

本論文では、外部バイアス回路を必要としない異なるCDNを用いた、完全差動型DPCCIIの新規実現法を示す。DPCCIIは3ビットのデジタル制御コードワードによって調整される。提案するDPCCIIは、プログラミング範囲全体で定常待機電力、オフセット電圧、帯域幅、直線性を維持する。このDPCCIIを基本回路として六角形FPAAを構築した。FPAAはデジタル制御され、信号配線に相互接続ネットワークを使用しないことでチップ効率を向上させている。このFPAAは、WLAN/WiMAX受信機向け6次バターワース可変LPFの実現に用いられる。本論文の構成は以下の通りである：第2章で提案するDPCCIIベースFPAAを提示し、第3章で提案DPCCIIの実現方法を提案し、第4章で提案FPAAを用いた6次LPFのシミュレーションを行い、最後に第5章で結論を述べる。

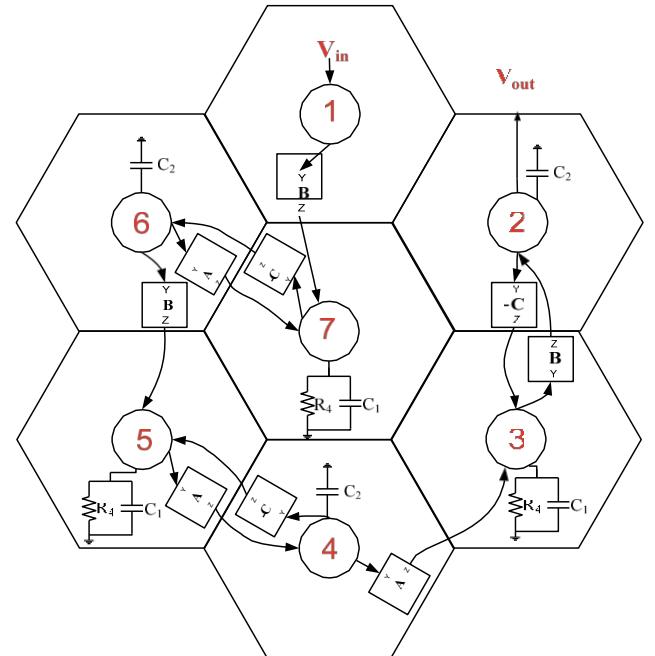

## 2. 提案するDPCCIIベースFPAAの実現

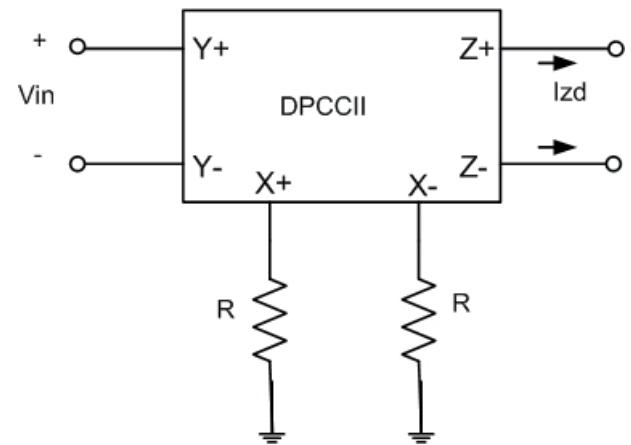

提案するFPAAは、DPCCIIに基づく7つのCABで構成される。DPCCIIは、X端子とZ端子を抵抗負荷に接続することで電圧モード能動回路として動作し、Y端子とZ端子がそれぞれ入力端子と出力端子として使用される。提案DPCCIIの主な利点は、コードワード「000」を用いてパラメータ「 $\alpha$ 」をゼロに設定することでオフにできる点である。したがって、異なるCAB間のプログラマブルスイッチは不要となる。CABはDPCCII内部に存在するCDNのMOSスイッチを介してオン/オフ可能である。

提案するFPAA構造は、FPAA[9]におけるグローバル相互接続配線の必要性を排除する。これにより信号経路の寄生容量が低減され、チップ全体の周波数応答が改善される。これは、CAB内部で使用される回路の出力をゼロに設定できる限り実現可能である。従来の設計[1-4]でスイッチを用いて実装されていた相互接続ネットワークを除去したこと、信号経路の総寄生容量が低減され、チップの周波数応答が改善された。

図2aにCAB基本回路を示し、図2bにFPAAアーキテクチャを示す。FPAAの端部に配置された6つのCABは3つのDPCCIIで構成され、中央のCABは6つのDPCCIIで構成される。FPAA端部のCABには「A」「B」「C」と命名された3つのDPCCIIが含まれる。簡略化のため、図2に示すようにCAB内部にはシングルエンドDPCCIIが配置されている。各CABの中心部では、差動ポートが入力電圧ポートまたは出力電流ポートとして使用される。この差動ポートは各CAB内部のDPCCIIのY端子に接続されている。CAB内部のDPCCIIのZ端子については、それぞれが隣接する別のCABの中心部に配置された差動ポートに接続されている。

隣接する別のCABの中央に位置する差動ポートに接続される。

図2a. CAB基本構成回路

図2b. 提案するDPCCIIベースのFPAAアーキテクチャ。

FPAA上でアクティブフィルタを実現するには、異なるフィルタ応答を実現するために負帰還接続が必要である。したがって、回路「C」の出力は負帰還を提供するために負の形で接続される。中央配置のCABについては、6つのDPCCII「A、B、C、D、E、F」で構成される。それらのY端子はCAB中央の差動ポートに接続され、Z端子は隣接する別のCABの差動ポートに接続される。

提案されたFPAAは、X端子とZ端子を抵抗負荷／容量負荷に接続するだけで、様々な電圧モードアナログ信号処理アプリケーションの設計にも利用可能である。各CABの差動ポートにおける合算電流は、FPAA出力電流信号として使用できる。出力ポートに接続された負荷に応じて、VGA、積分器、フィルタなど様々なアナログ信号処理アプリケーションを実現可能である。

はFPAの出力電流信号として利用可能である。出力ポートに接続する負荷に応じて、可変ゲインアンプ（VGA）、積分器、フィルタなど様々なアナログ信号処理アプリケーションを実現できる。チップ外に配置する受動負荷を選択することで、大幅な面積削減が可能となり、チップのI/Oピン数を増加させることもない。負荷の実装はFPAユーザーに任意に委ねられており、負荷をプログラマブルにするか固定値にするかを選択可能である。負荷をプログラマブルに選択した場合、調整精度は大幅に向かう。提案するFPAは合計14個のI/Oピンを有する。CAB内部のDPCCIIはシフトレジスタ(SR)とインバータを用いてプログラミングされる。各DPCCIIは3ビットのコードワードとその補数を用いてプログラミングされる。エッジドCABのプログラムにはシリアル9ビットSRが、センタードCABには18ビットSRが使用される。この制御方式によりFPAチップに7ピンが追加される。提案するFPAと[9]のものを比較すると、チューニング方式ははるかに簡素化され、外部バイアス電圧の保存や生成が不要である。さらに消費電力も大幅に改善されている。

### 3. 提案するDPCCIIの実現

#### 3.1 プログラマブル電流コンベアのレビュー

CCIIのシングルエンドおよび完全差動構成の多くの実現例が提案されている[5]、[6]。CCIIは、必要なI-V特性を達成するために電圧フォロアと電流フォロアをカスケード接続することで設計できる。プログラマブルCCIIを設計するために、2つのアプローチが用いられた。最初のアプローチは、電流ミラーを用いてZポートの電流をスケーリングする方法である[8]。しかし、この手法はトランジスタの不一致問題に悩まされた。二つ目は、電流フォロアと直列に電流分割ネットワーク（CDN）を追加する方法である。これにより、Zポート電流はXポート電流のスケールされたコピーとなる[7]。

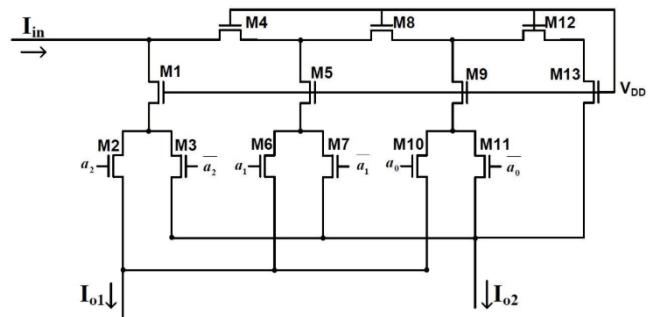

CDNはカスケード接続された $n$ 個の電流分割セルで構成される。各セルは流入電流を2分割する。半分は次のセルへ、もう半分はデジタルビットとその補数で制御される2つの並列MOSスイッチのいずれかに流れる。最終的に、ビット $a_n$ で制御される全セルの電流が加算されCDNの第1出力電流 $I_{o1}$ となる。

一方、 $a_n$ で制御されるスイッチと最終セル電流は加算され、CDNの第2出力電流

$I_{o2}$ となる。CDN出力電流値と電流プログラミング係数は以下のように与えられる：

$$I_{o1} = \alpha I_{in}, \quad (2)$$

$$I_{o2} = (1 - \alpha) I_{in}, \quad (3)$$

$$\alpha = \frac{1}{2^n} \sum_{i=0}^n 2^i a_i. \quad (4)$$

電流分割係数 $\alpha$ は、CDNに印加されるデジタルコードワード $a_{n-0}$ によって変化する。[7]で使用されたCDNは、定電流源を用いてバイアスされた差動増幅器（DA）に基づいていた。DAのゲート電圧が同じ状態で入力電流がDAのソースに注入されると、入力電流はDAのトランジスタ間で均等に分割される。[7]のCDNの主な欠点は、回路消費電力の増加を招く電流源の使用である。さらに、DAが飽和領域に留まるよう、各コードワードごとにDAのゲート電圧を調整する必要がある。以下の節では、[10]に記載された2つの完全差動CCIIと3ビットMOSラダーCDNを用いて、新たに提案されたデジタルプログラマブルCCII（DPCCII）を設計する。

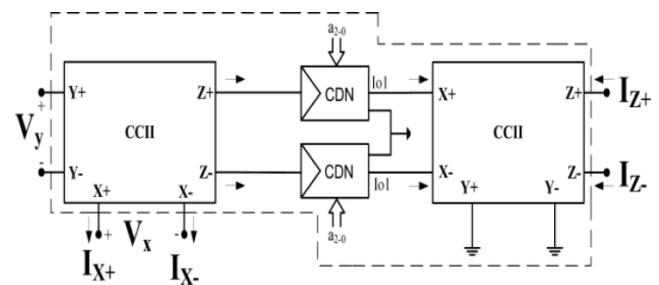

#### 3.2 新規DPCCIIの実現

提案されたDPCCIIのブロック図を図3に示す。この回路は、2つの完全差動CCIIと2つの3ビットMOSラダーCDNで構成される。最初のCCIIはYポートに印加された差動電圧をXポートに伝達し、接地抵抗 $R$ を用いて電流に変換する。その後、Xポートの電流はZポートに伝達される。この電流は3ビットMOSラダーCDNに流入する。電流分割比はCDNに印加されるデジタルコードワード $a_{(2)}, a_{(1)}, a_0$ に応じて変化する。

図3. 提案DPCCIIブロック図

CDNは図4に示す通り、抵抗器とスイッチを同時に機能するMOSトランジスタのみで構成される。このCDNにおける電流分割原理

図4. 3ビットMOS CDNの回路図。

は、等価抵抗値が

各セル出力ノード（接続されたもの）で観測される等価抵抗値に依存する。次のセルとスイッチへのセルは、MOSトランジスタの直流動作モードにおいて等しい不均一性を有する。

MOSトランジスタの直流動作モードにおいて、これらは等価である。こ

これは出力電流ノード  $I_{o1}$  および  $I_{o2}$  の電位をゼロに設定した場合にのみ達成可能である[10]。したがって、CDN出力における仮想接地条件を満たすため、Xポートが CDN の最初の出力ノードに接続された別の接地YポートCCIIが使用される。このXポートの差動電流はZポート電流に伝達され、Yポートの差動電圧とZポートの差動電流の関係は式(5)で与えられる。この提案された実現に用いられたCCII回路は[11]に記載されている。

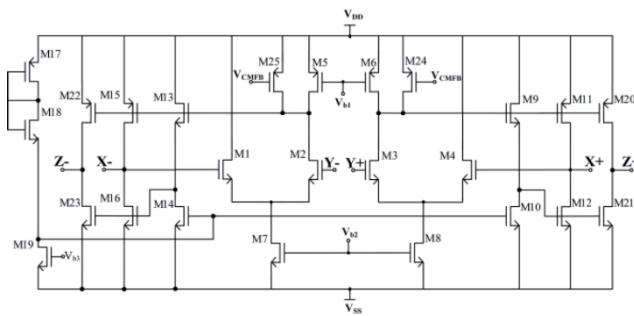

$$I_z = \alpha I_x = \frac{\alpha}{R} V_{y-} - V_{y+} \quad (5)$$

使用したCCIIを図5に示す。この回路は、M1-M2とM3-M4で構成される2つの差動増幅器 (DA) から成る。各DAのトランジスタ1つは最高電圧電源に接続され、もう1つのトランジスタは定電流源M5-M6に接続されている。2つのDAはM7-M8で構成された電流源を用いてバイアスされる。電圧追従動作は、2つのDAに同じ差動電流とコモンモード電流を強制することで実現される。電流追従動作は、クラスAB出力段M11-M12、M20-M21、M15-M16、M22-M23を介して行われる。出力段の待機電流は、トランジスタM9-M10、M13-M14、M17-19によって制御される。この回路は[11]で提案されたものである。本研究ではCCIIを階層構造で使用するため、出力端子のコモンモード値を制御する必要があった。この目的のためにトランジスタM24-M25が2つ使用されている。出力電圧値を調整するための電圧信号  $V_{CMFB}$  を生成するために、古典的なコモンモードフィードバック回路が使用されている。

図5. CCII回路図 [11]。

DPCCIIは、 $\pm 0.5$  Vの平衡電源電圧下で、90nm TSMC CMOS技術モデルを用いてVirtuosoにより設計・シミュレーションされた。CCIIトランジスタのアスペクト比を表1に示す。DPCCIIは、コードワード  $a_{(2)}$ 、 $a_{(1)}$ 、 $a_0$  を変化させながらテストされた。

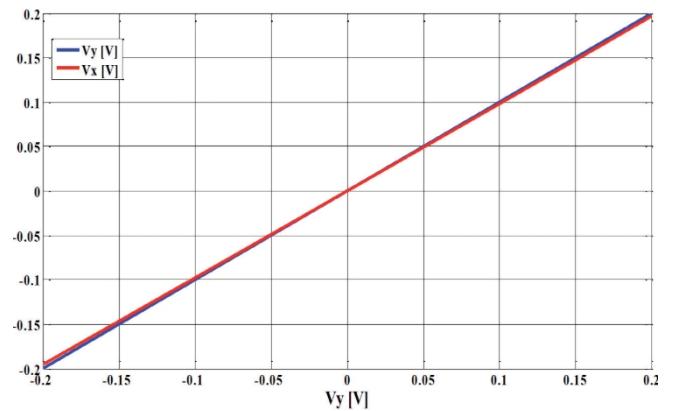

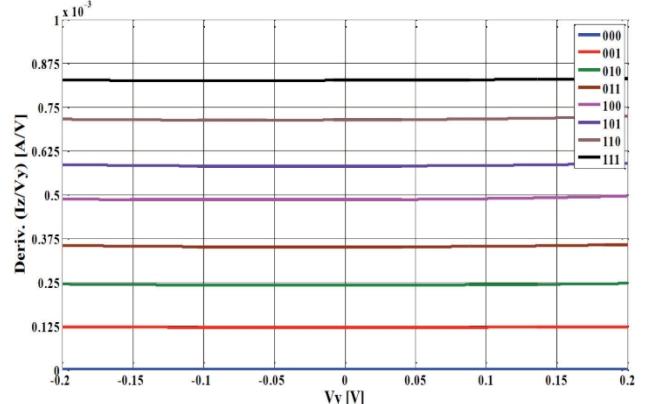

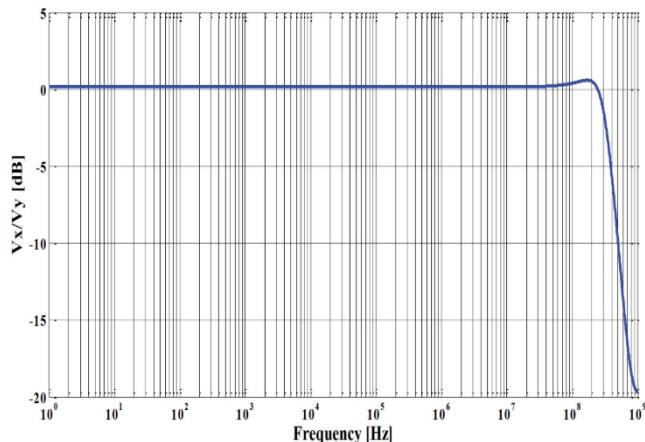

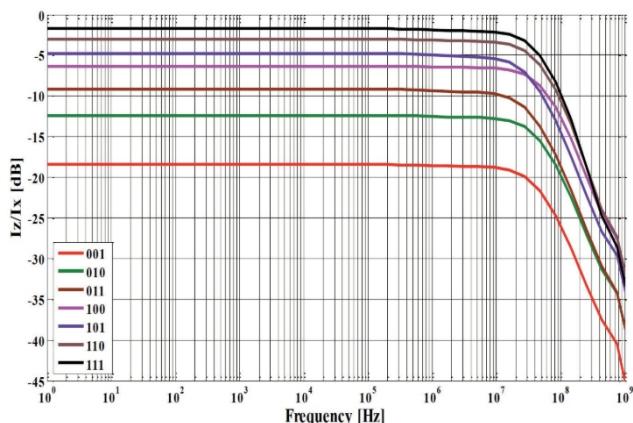

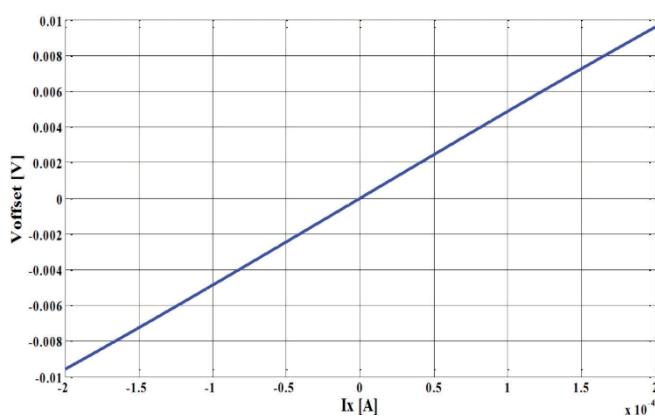

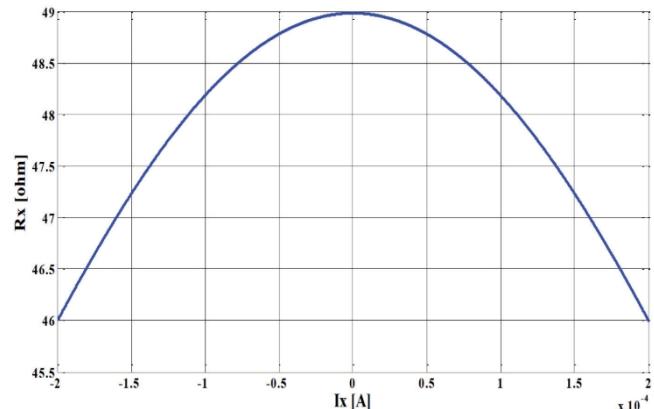

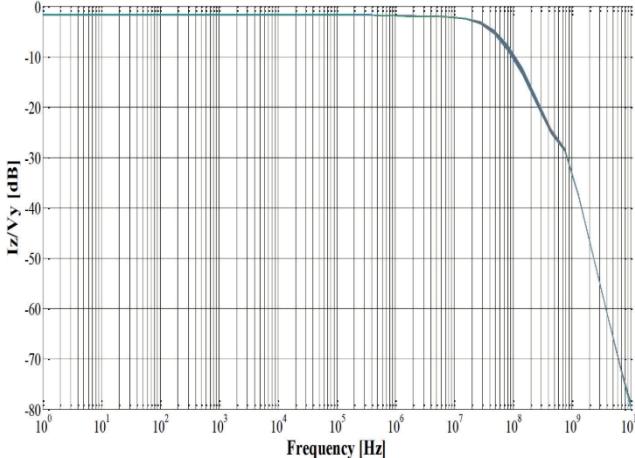

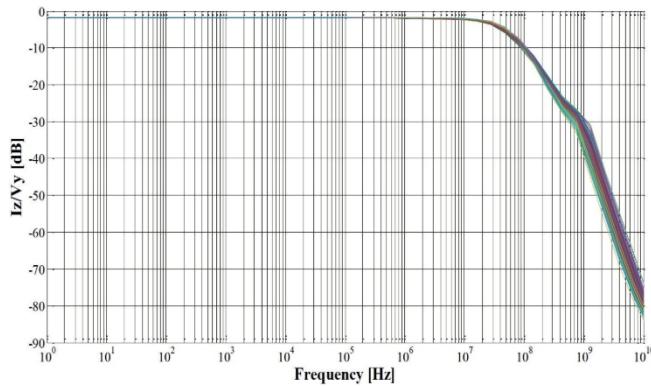

デジタルビットの「1」と「0」はそれぞれ0.5 Vおよび提案されたDPCCIIは0.6 mWで定常待機電力を有する。電圧利得開放帯域幅と電流利得短絡帯域幅もそれぞれ340 MHzと540 MHzで一定である。X端子オフセット電圧と有限出力抵抗はそれぞれ10mV未満、49Ω未満であり、全コードワード組み合わせで一定である。開放負荷下におけるY端子とX端子間の電圧伝達動作を図6に示す

図6に示され、短絡負荷下 (-Y接地) におけるX端子とZ端子間の可変電圧伝達作用の微分は図7に示す。

| トランジスタ             | W(μm) | L(μm) |

|--------------------|-------|-------|

| M1, M2, M3, M4     | 15    | 0.36  |

| M5, M6             | 0.18  | 0.18  |

| M7, M8             | 10    | 0.54  |

| M9, M10, M13, M14  | 1     | 0.9   |

| M11, M15, M20, M22 | 30    | 0.36  |

| M12, M16, M21, M23 | 15    | 0.36  |

| M17                | 28    | 0.18  |

| M18                | 14    | 0.18  |

| M19                | 20    | 0.36  |

| M24, M25           | 0.18  | 0.18  |

表1. 模擬CCIIのアスペクト比

図6. Y端子とX端子間の電圧伝達作用。

図7. Z端子電流とY端子電圧の比の微分係数。

電圧伝達動作は $\pm 0.2$  Vの範囲で実現され、電流プログラミングは $\pm 200$   $\mu$ Aの範囲で達成される。

DPCCIIの電圧利得と電流利得の振幅応答をそれぞれ図8および図9に示す。X端子におけるオフセット電圧と有限抵抗をそれぞれ図10および図11に示す。電圧利得の3次高調波歪みを異なるコードワード組み合わせで測定した。Y端子入力電圧1 MHz、200 mVppにおいて、コードワードを変化させながらZ端子電流のHD<sub>3</sub>を測定した。

シミュレーション結果を表2に示す。異なるコードワードにおけるZ端子電流のHD<sub>3</sub>は-47.9 dBを下回っている。

図8. Y端子とX端子間の電圧伝達作用の振幅応答。

図9. X端子とY端子間の電流プログラミングの振幅応答。

図10. X端子におけるオフセット電圧。

図11. X端子における有限抵抗値。

| コードワード<br>$a_2a_1a_0$ | $\alpha$ 理論値 | $\alpha$ シミュレーション | HD <sub>3</sub> [dB] |

|-----------------------|--------------|-------------------|----------------------|

| 000                   | 0            | 5e-12             | -                    |

| 001                   | 0.125        | 0.121             | -51.8                |

| 010                   | 0.25         | 0.241             | -48.57               |

| 011                   | 0.375        | 0.351             | -47.9                |

| 100                   | 0.5          | 0.485             | -51.9                |

| 101                   | 0.625        | 0.581             | -56.9                |

| 110                   | 0.75         | 0.713             | -55.4                |

| 111                   | 0.875        | 0.826             | -61.7                |

表2. Z端子電流分割係数とそのHD<sub>3</sub>。

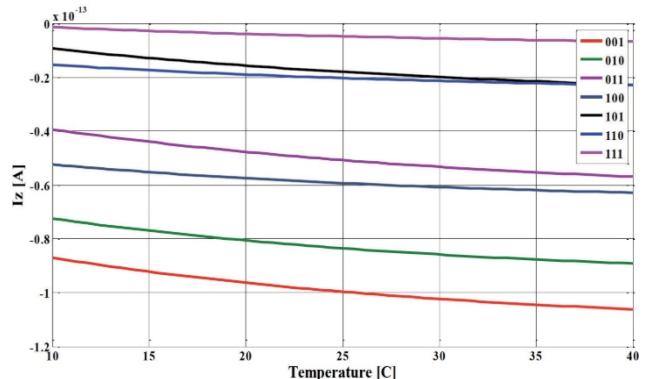

コードワードを変化させながら、DPCCII Z端子電流に対する温度変動の影響を試験した。図12に示すように、差動電流変動は107 fAから4 fAの範囲であった。

図12. 温度による差動Z電流の変動

| パラメータ                  | 本研究        | 文献[7]の研究 |

|------------------------|------------|----------|

| 技術                     | 0.09 μm    | 0.5 μm   |

| 電源                     | ±0.5V      | ±1.5V    |

| 電圧伝送範囲<br>電圧供給からの<br>% | 40%        | 66.6     |

| 消費電力                   | 0.6mW      | 2.7mW    |

| THD @200mV-1<br>MHz    | 以下<br>47dB | -40dB未満  |

表3. 提案したDPCCIIと先行研究の比較

モンテカルロシミュレーションを実施し、Z端子微分電流とX端子微分電流の比が20%

図13に示すように、ミスマッチングおよびプロセス変動に対するおよび14にそれぞれ示されるように、不整合およびプロセス変動が生じている。 $\alpha$ の値は0.875である。シミュレーションから見て取れるように、変動は非常に小さい。

図13. 20%のミスマッチ誤差に対する、微分Z電流と微分X電流の変化の比率。

図14. 20%の工程変動に対する微分Z電流と微分X電流の変化量の比率

提案された実現方式と[7]に示された方式の比較を表3に示す。提案方式の消費電力は[7]の方式よりも大幅に小さい。提案手法の3dB帯域幅もより広い。入力電圧振幅が200mVppの動作周波数1MHzにおいて、全高調波歪率は-47dB未満であり、[7]の値を上回る。

#### 4. 第六次バターワース可変LPF

提案するFPAAを用いて、6次バターワース可変電圧モードLPFを実現する。フィルタは3つの2次バイクワッドセクションをカスケード接続する手法[12]で設計した。フィルタは図15に示すようにFPAA上にマッピングされる。バイクワッドの伝達関数、カットオフ周波数

周波数、品質係数、直流利得に対する変動を検証するため、モンテカルロシミュレーションを実施した。

$$\frac{V_{out}}{V_{in}} = \frac{\frac{\alpha_1 \alpha_2}{R_1 R_2 C_1 C_2}}{S^2 + S \frac{1}{R_4 C_1} + \frac{\alpha_2 \alpha_3}{R_2 R_3 C_1 C_2}}, \quad (6)$$

$$\omega_o = \sqrt{\frac{\alpha_2 \alpha_3}{R_2 R_3 C_1 C_2}}, \quad (7)$$

$$Q = R_4 \sqrt{\frac{\alpha_2 \alpha_3 C_1}{R_2 R_3 C_2}}, \quad (8)$$

$$\frac{V_{out}}{V_{in} S=0} = \frac{\alpha_1 R_3}{\alpha_3 R_1} \quad (9)$$

図15. FPAA上にマッピングされた6次DPCCIIベースLPF

WLAN/WiMAX受信機のカットオフ周波数は8.1MHzから13.5MHzの範囲である。提案フィルタのカットオフ周波数は $\alpha_2$ を変化させることで調整可能であるが、フィルタの品質係数も変化する。設計パラメータの選択例： $R_1 = R_2 = R_3 = R_4 = R$ ,  $C_2 = 3C_1$ ,  $\alpha_1 = \alpha_3 = 0.875$ 。

入力電圧はCAB1に印加され、出力はCAB2から取り出される。2次回路セクションは回路「B1, C7, A6」、「B6, A5, C4」、「A4, B3, C2」にマッピングされる。

抵抗RはDPCCIIのX端子に接続されたものです。FPAAはフィルタをマッピングしてシミュレートされ、R、C<sub>1</sub>、C<sub>2</sub>は以下の値で選択されています：

1.1 kΩ、2 pF、6 pFである。電流プログラミング係数 $\alpha_1$ 、 $\alpha_2$ 、 $\alpha_3$ は、それぞれ回路「B1、B6、A4」、「C7、A5、B3」、「A6、C4、C2」に対応する。カットオフ周波数の調整は $\alpha_{(2)}$ を変化させることで行われる。 $\alpha_1$ と $\alpha_3$ の値は直流利得0.875を得るために0.875に設定された

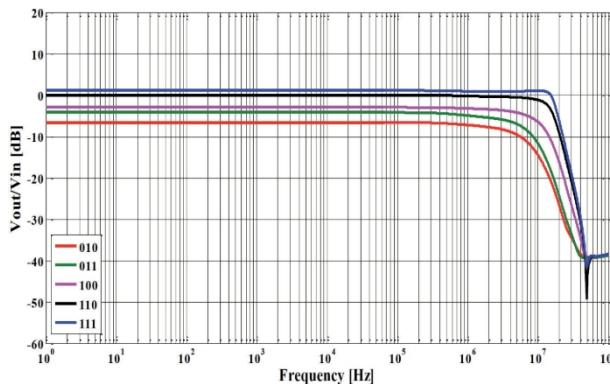

0 dBとなるように選択されている。フィルタの振幅応答を図16に示す。フィルタのシミュレーション結果の概要を表4に示す。フィルタのカットオフ周波数における出力帰一化雑音密度を測定した。

図16. 第6次可変LPFの振幅応答。

| コードワード<br>a2a1a0 | f <sub>o</sub><br>[MHz] | 直流<br>利得[dB] | ノイズ<br>[nV/√Hz] |

|------------------|-------------------------|--------------|-----------------|

| 010              | 5.2                     | -6.6         | 108             |

| 011              | 6.2                     | -4.1         | 141             |

| 100              | 8.5                     | -3           | 100             |

| 110              | 13.9                    | 0            | 104             |

| 111              | 16.9                    | 1.2          | 100             |

表4. 提案フィルタのシミュレーション結果。

## 5. 結論

新たに提案されたFPAAを導入する。提案されたFPAAは相互接続ネットワークを使用しないため、高周波アプリケーションの実現に利用できる。FPAAは六角格子状に配置された7つのCABで構成される。CABはデジタル制御完全差動電流コンペア(DPCCII)を用いて設計され、待機電力は合計14.4 mWである。DPCCII回路は、全調整範囲において待機電力0.6 mW、帯域幅100 MHz、オフセット電圧2 mV@500 μA、全調整範囲で200 mV-1 MHzにおけるTHDが-47 dB未満という特性を有する。DPCCIIを用いて、総待機電力14.4 mWの六角形FPAAを実現した。このFPAAは、WLAN/WiMAX受信機向け6次可変バターワースLPFの実現に用いられる。フィルターのカットオフ周波数は5.2 MHzから16.9 MHzまで調整される。

## 参考文献

- [1] MAHMOUD, S. A. デジタル制御CMOS平衡出力トランジスタと可変利増幅器および $g_m$ -C フィルタへの応用 (FPGA上)。 *Journal of Circuits, Systems and Computers*, 2005, vol. 14, p. 667-684.

- [2] ルービー, C. A., ライデン, C. オペアンプベースのCMOSフィールドプログラマブルアナログアレイ。 *IEEE回路・デバイス・システム学会論文集*, 2000, p. 93-95.

[3] GAUDET, V. C., GULAK, P. G. 電流コンペアベースのフィールドプログラマブルアナログアレイのCMOS実装。 *信号・システム・コンピュータ会議論文集*, 1997, p. 1156.

[4] MAHMOUD, S. A., SOLIMAN, E. A. 低電圧電流コンペアベースのフィールドプログラマブルアナログアレイ。 *Journal of Circuits, Systems, and Computers*, 2011, vol. 20, p. 1677-1701.

[5] SMITH, K. C., SEDRA, A. 電流コンペアー新しい回路構成要素。 *IEEE論文集*, 1968年, 第56巻, p. 1368-1369.

[6] セドラ, A., スミス, K. C. 第二世代電流コンペアとその応用, *IEEE回路理論学会誌* 1970, 第17巻, p. 132-134

[7] MAHMOUD, S. A., HASHIESH, M. A., SOLIMAN, A. M. 低電圧デジタル制御完全差動電流コンペア。 *IEEE Trans. on Circuits and Systems I*, 2005, vol. 52, p. 2055-2064.

[8] HASSAN, T. M., MAHMOUD, S. A. 新しいデジタルプログラマブルCMOS CCIIに基づく独立したゲイン- $\omega_0$ -Q制御を備えた完全プログラマブルユニバーサルフィルタ。 *Journal of Circuits, Systems and Computers*, 2009, vol. 18, p. 875-897.

[9] BECKER, J., HENRICI, F., TRENDELENBURG, S., ORTMANZ, M., マンロイ, Y. 六方格子構造における55個のデジタル可変OTAからなるフィールドプログラマブルアナログアレイ。 *IEEE J. Solid-State Circuits*, 2008, vol. 43, p. 2759-2768.

[10] BULT, K., GEELEN, G. J. 本質的に線形かつコンパクトなMOST専用電流分割技術。 *IEEE J. Solid-State Circuits*, 1992, vol. 27, p. 1730-1735.

[11] MAHMOUD, S. A., AWAD, I. A. 完全差動CMOS電流フィードバックオペアンプ。 *Analog Integrated Circuits and Signal Processing*, 2005, vol. 43, p. 61-69.

[12] OSKOOEI, M. S., MASOUMI, N., KAMAREI, M., SJÖLAND, H. A. CMOS 4.35-mW +22-dBm IIP3 連続可変チャンネル選択フィルタ WLAN/WiMAX レシーバ用。 *IEEE J. Solid-State Circuits*, 2011, vol. 46, p. 1382-1391.

## 著者について...

ソリマン・マフムードは1971年、エジプトのカイロに生まれた。1994年に学士号（優等）、1996年に修士号、1999年に博士号を、いずれもエジプト・カイロ大学電子通信学部で取得した。2005年には科学技術アカデミーより先端工学技術分野の科学賞を授与された。2008年夏と2009年夏にはドイツのウルム大学に客員研究員として滞在。2008年9月から2010年1月まで、エジプト・ファイユーム大学電子通信工学科の教授兼学科長を務めた。現在はファイユーム大学を休職し、シャルジャ大学で勤務中。

マフムード教授は国際学術誌・会議で100本以上の論文を単独・共著で発表している。著書に『差動差分オペアンプ設計』（ISBN 978-3-639-17849-4、VDM出版社）がある。研究・教育分野は回路理論、完全集積アナログフィルタ、高周波トランズコンダクタンス増幅器、低電圧アナログCMOS回路設計、電流モードアナログ信号処理、混合アナログ/デジタルプログラマブルアナログブロック。

プログラム可能なアナログブロックである。マフムード教授は IEEEシニアメンバーである。2012年4月、マフムード教授は2011-2012年度の業績によりシャルジャ大学研究賞を受賞した。

エマン・ソリマンは1984年エジプト・カイロ生まれ。2006年に学士号（優等）、2008年に修士号、2012年に博士号を

現在、カイロ・ドイツ大学（エジプト・カイロ）電子工学科助教。研究分野は回路理論、低電圧アナログCMOS回路設計、電流モードアナログ信号処理、およびFPGA（フィールドプログラマブルゲートアレイ）上の混合/デジタル応用。